|

Электротехника

| |

| SlaVe4U | Дата: Среда, 12.01.2011, 03:16 | Сообщение # 31 |

|

Главный Администратор

Группа: Администраторы

Сообщений: 320

Награды: 23

Репутация: 222

Статус: Offline

| Микросхема ИЕ14 (рис. 42) во многом напоминает микросхему ИЕ2. Она также содержит счетный триггер с входом С2. При соединении выхода 1 счетного триггера (вывод 5) с входом С2 образуется двоично-десятичный счетчик, работающий в коде 1-2-4-8. Срабатывание триггера и делителя на 5 происходит по спадам импульсов положительной полярности. Различие с микросхемой ИЕ2 заключается в полярности импульсов сброса - триггеры микросхемы ИЕ14 устанавливаются в 0 при подаче на вход R лог. 0. Кроме того, в микросхеме ИЕ14 есть возможность предварительной установки триггеров счетчика. Для установки триггеров необходимый код следует подать на входы D1 - D8, а на вход L - импульс отрицательной полярности. При лог. 0 на входе L сигналы на выходах 1-8 повторяют сигналы на входах D1 - D8, при лог. 1 происходит запоминание и возможен счетный режим работы микросхемы

Микросхему можно использовать в счетчиках с предварительной установкой, например, в цифровых шкалах радиоприемников и трансиверов с учетом промежуточной частоты.

Микросхема ИЕ15 (рис. 42) по своей структуре и функционированию аналогична микросхеме ИЕ14, но делитель с входом С2 делит частоту на 8,

Микросхемы КР531ИЕ16 и КР531ИЕ17 - реверсивные синхронные четырехразрядные счетчики - двоично-десятичный и двоичный соответственно. Разводка их выходов совпадает (рис. 43), более того, она совпадает с разводкой микросхем ИЕ9 и ИЕ10, за исключением вывода 1, для описываемых микросхем это вход изменения направления счета

U/D, вход сброса отсутствует. При лог. 1 на входе U/D счетчик считает вверх, при лог. 0 - вниз. Синхронная параллельная запись информации в микросхемы КР531ИЕ16 и КР531ИЕ17 происходит со входов D1 - D8 по спаду тактового импульса отрицательной полярности на входе С и подаче лог. 0 на вход разрешения загрузки EL. При счете на входе EL должна быть лог. 1.

Отличием описываемых микросхем от ИЕ9 и ИЕ10 является также полярность сигналов разрешения переноса ЕР и разрешения счета ЕС (для разрешения работы на эти входы необходимо подать лог. 1). Соответственно выходным разрешающим сигналом на выходе переноса Р является лог. 0, он появляется в случае, когда микросхема КР531ИЕ16 досчитала до состояния 9 (КР531ИЕ17 - до состояния 15) при прямом счете или до 0 при обратном, а на входе разрешения переноса ЕР - лог. 0.

Примеры соединения микросхем КР531ИЕ16 и КР531ИЕ17 в многоразрядный счетчик приведены на рис. 44 и 45. При соединении микросхем по схеме рис. 44 максимальная частота счета снижается по отношению к максимально возможной для одной микросхемы, при соединении по схеме рис. 45 - не снижается. Следует помнить, что переключение направления счета на входе U/D и смену информации на входах ЕР и ЕС следует производить в паузе между тактовыми импульсами, то есть при лог. 1 на входах С микросхем или в момент изменения сигнала на этих входах с лог. 0 на лог. 1. Входной ток микросхем по входу ЕР в состоянии лог. 0-4 мА. Микросхема ИЕ18 (рис. 46) аналогична по функционированию микросхеме ИЕ11, но ее коэффициент пересчета равен 16.

Рассмотренные выше микросхемы счетчиков серии КР531 имеют входные токи по управляющим входам, как правило, больше стандартных. При подаче на входы лог. 0 токи составляют для микросхем КР531ИЕ9 и КР531ИЕ10 по выводу 2 - 5 мА, выводу 10-3 мА, выводу 9-4 мА. Для микросхем КР531ИЕ11 и КР531ИЕ18 ток по вы

воду 10 составляет 4 мА, а для КР531ИЕ14 и КР531ИЕ15 ток по выводу 8-8 мА, по выводу 6-10 мА, по выводам 1, 3, 4, 10, 11, 13 - 0,75 мА.

Микросхема К555ИЕ19 - два четырехразрядных двоичных счетчика (рис. 47), каждый из которых имеет два входа: R - для установки триггеров счетчика в 0 при подаче на вход R лог. 1 и С - для подачи счетных импульсов. Срабатывание триггеров счетчика происходит по спадам импульсов положительной полярности, подаваемых на вход С,

выходной код счетчиков - стандартный, 1-2-4-8. Для соединения счетчиков в многоразрядный выходы 8 предыдущих разрядов необходимо соединить со входами С последующих.

Микросхема К555ИЕ20 (рис. 47) -два четырехразрядных двоично-десятичных счетчика, каждый из которых аналогичен счетчику микросхем ИЕ2, за исключением входов установки в 0 R.

Каждый счетчик имеет триггер со входом С1, выходом 1 и делитель частоты на 5 со входом С2 и выходами 2,4,8. Триггер и счетчик срабатывают по спадам положительных импульсов, подаваемых на входы С1 и С2, на входе R при счете должен быть лог. 0. Для получения десятичного счетчика выход 1 надо соединить со входом С2, при этом код счетчика будет 1-2-4-8. Если же выход 8 соединить со входом С1, входные импульсы подать на вход С2, выходной код будет 1-2-4-5, а на выходе 1 сигнал будет иметь форму меандра с частотой, в 10 раз меньше входной. Впрочем, так же можно соединять счетчики микросхем ИЕ2 и ИЕ14. Предельная частота работы триггера - 25 МГц, делителя на 5 - 20 МГц.

|

| |

| |

| SlaVe4U | Дата: Среда, 12.01.2011, 03:18 | Сообщение # 32 |

|

Главный Администратор

Группа: Администраторы

Сообщений: 320

Награды: 23

Репутация: 222

Статус: Offline

| 29

http://pda.coolreferat.com/Синтез_счетчиков_импульсов

У этого термина существуют и другие значения, см. Счётчик.

$IMAGE1$

Двухразрядный двоичный счётчик с последовательной организацией переноса на T-триггере.

$IMAGE2$

4-х битный синхронный последовательный счётчик использующий T-триггеры

Счётчик числа импульсов — устройство, на выходах которого получается двоичный(двоично-десятичный) код, определяемый числом поступивших импульсов. Счётчики могут строиться на T-триггерах. Основной параметр счётчика — модуль счёта — максимальное число единичных сигналов, которое может быть сосчитано счётчиком. Счётчики обозначают через СТ (от англ. counter).

Счётчики классифицируют:

по числу устойчивых состояний триггеров

на двоичных триггерах

на троичных триггерах

на n-ичных триггерах

по модулю счёта:

двоично-десятичные (декада);

двоичные;

с произвольным постоянным модулем счёта;

с переменным модулем счёта;

по направлению счёта:

суммирующие;

вычитающие;

реверсивные;

по способу формирования внутренних связей:

с последовательным переносом;

с параллельным переносом;

с комбинированным переносом;

кольцевые;

по способу переключения триггера:

синхронные;

асинхронные;

Счётчик Джонсона

Двоичные счетчики

Схему двоичного счетчика можно получить с помощью формального синтеза, однако более наглядным путем представляется эвристический. Таблица истинности двоичного счетчика — последовательность двоичных чисел от нуля до 2n − 1, где n - разрядность счётчика. Наблюдение за разрядами чисел, составляющих таблицу, приводит к пониманию структурной схемы двоичного счетчика. Состояния младшего разряда при его просмотре по соответствующему столбцу таблицы показывают чередование нулей и единиц вида 01010101..., что естественно, т. к. младший разряд принимает входной сигнал и переключается от каждого входного воздействия. В следующем разряде наблюдается последовательность пар нулей и единиц вида 00110011... . В третьем разряде образуется последовательность из четверок нулей и единиц 00001111... и т.д. Из этого наблюдения видно, что следующий по старшинству разряд переключается с частотой, в два раза меньшей, чем данный. Известно, что счетный триггер делит частоту входных импульсов на два. , Сопоставив этот факт с указанной выше закономерностью, видим, что счетчик может быть, построен в виде цепочки последовательно включенных счетных триггеров. Заметим, кстати, что согласно ГОСТу входы элементов изображаются слева, а выходы справа. Соблюдение этого правила ведет к тому, что в числе, содержащемся в счетчике, младшие разряды расположены левее старших.

Двоичные счетчики с параллельным переносом

|

| |

| |

| SlaVe4U | Дата: Среда, 12.01.2011, 03:18 | Сообщение # 33 |

|

Главный Администратор

Группа: Администраторы

Сообщений: 320

Награды: 23

Репутация: 222

Статус: Offline

| Выше рассмотрены схемы двоичных последовательных счетчиков, то есть таких счетчиков, в которых при изменении состояния определенного триггера возбуждается последующий триггер, причем триггеры меняют свои состояния не одновременно, а последовательно. Если в данной ситуации должны изменить свои состояния n триггеров, то для завершения этого процесса потребуется n интервалов времени, соответствующих времени изменения состояния каждого из триггеров. Такой последовательный характер работы является причиной двух недостатков последовательного счетчика: меньшая скорость счета по сравнению с параллельными счетчиками и возможность появления ложных сигналов на выходе схемы. В параллельных счетчиках синхронизирующие сигналы поступают на все триггеры одновременно. Последовательный характер переходов триггеров счетчика является источником мощных сигналов на его выходах. Например, в счетчике, ведущем счет в четырехразрядном двоичном коде с “весами” 8-4-2-1, при переходе от числа 710 = 01112 к числу 810 = 10002 на выходе появится следующая последовательность сигналов: 0111 ->ð 0110 ->ð 0100 ->ð 0000 ->ð 1000 Это означает, что при переходе из состояния 7 в состояние 8 на входах счетчика на короткое время появятся состояния 6; 4; 0. Эти дополнительные состояния могут вызвать ложную работу других устройств. С целью уменьшения времени протекания переходных процессов можно реализовать счетчик в варианте с подачей входных импульсов одновременно на все триггеры. В этом случае получим счетчик с параллельным переносом. Здесь на информационные входы триггеров подаются сигналы, являющиеся логической функцией состояния счетчика и определяющие конкретные триггеры, которые изменяют свое состояние при данном входном импульсе. Принцип стробирования сводится к следующему: триггер меняет свое состояние при пропускании очередного импульса синхронизации, если все предыдущие триггеры находились в состоянии логической единицы. Параллельные счетчики имеют более высокое быстродействие по сравнению с последовательными, поскольку синхронизирующие импульсы поступают на все триггеры одновременно. Максимальным быстродействием обладают синхронные счетчики с параллельным переносом, структуру которых найдем эвристически, рассмотрев процессы прибавления единицы к двоичным числам и вычитания ее из них.

Счетчики с последовательно-параллельным переносом

В связи с ограничениями на построение счетчиков с параллельным переносом большой разрядности широкое распространение получили счетчики с групповой структурой, или счетчики с последовательнопараллельным переносом. Разряды таких счетчиков разбиваются на группы, внутри которых организуется принцип параллельного переноса. Сами же группы соединяются последовательно с использованием конъюнкторов, формирующих перенос в следующую группу при единичном состоянии всех триггеров предыдущих. При единичном состоянии всех триггеров группы приход очередного входного сигнала создаст перенос из этой группы. Эта ситуация подготавливает межгрупповой конъюнктор к прямому пропусканию входного сигнала на следующую группу.

В наихудшем для быстродействия случае, когда перенос проходит через все группы и поступает на вход последней,

tУСТ = t • (ĺ — 1) + tГР

где ĺ — число групп, tГР — время установления кода в группе.

В развитых сериях ИС обычно имеется по 5…10 вариантов двоичных счетчиков, выполненных в виде 4-х разрядных групп (секций). Каскадирование секций может выполняться путем их последовательного включения по цепям переноса, организации параллельно-последовательных переносов или для более сложных счетчиков с двумя дополнительными управляющими входами разрешения счета и разрешения переноса путем организации параллельных переносов и в группах и между ними. Особенностью двоичных счетчиков синхронного типа является наличие ситуаций с одновременным переключением всех его разрядов (например, для суммирующего счетчика при переходе от кодовой комбинации 11…1 к комбинации 00…0 при переполнении счетчика и выработке сигнала переноса). Одновременное переключение многих триггеров создает значительный токовый импульс в цепях питания ЦУ и может привести к сбою в их работе. Поэтому в руководящих материалах по использованию некоторых БИС/СБИС программируемой логики, в частности, имеется ограничение на разрядность двоичных счетчиков заданной величиной k (например, 16). При необходимости применения счетчика большей разрядности рекомендуется переходить к коду Грея, для которого переходы от одной кодовой комбинации к другой сопровождаются переключением всего одного, разряда. Правда, для получения результата счета в двоичном кода придется использовать дополнительно преобразователь кода, но это является платой, за избавление от токовых импульсов большой интенсивности в цепях питания.

|

| |

| |

| SlaVe4U | Дата: Среда, 12.01.2011, 03:21 | Сообщение # 34 |

|

Главный Администратор

Группа: Администраторы

Сообщений: 320

Награды: 23

Репутация: 222

Статус: Offline

| 30

Счетчиком называют цифровое устройство, обеспечивающее подсчет числа электрических импульсов. Коэффициент пересчета счетчика равен минимальному числу импульсов, поступивших на вход счетчика, после которых состояния на выходе счетчика начинают повторяться. Счетчик называют суммирующим, если после каждого очередного импульса цифровой код на выходе счетчика увеличивается на единицу. В вычитающем счетчике после каждого импульса на входе счетчика цифровой код на выходе уменьшается на единицу. Счетчики, в которых возможно переключение с режима суммирования на режим вычитания, называются реверсивными.

Счетчики могут быть с предварительной установкой. В таких счетчиках информация с входов предварительной установки передается на выходы счетчика по сигналу на специальном входе предварительной установки. По своей структуре счетчики делятся на последовательные, параллельные и параллельно-последовательные. Последовательный двоичный счетчик образован цепочкой последовательно включенных счетных триггеров. В параллельном счетчике счетные импульсы подаются одновременно на входы всех разрядов счетчика. Параллельные счетчики имеют большее быстродействие по сравнению с последовательными. Параллельно-последовательные счетчики имеют высокое быстродействие и большое значение коэффициента пересчета.

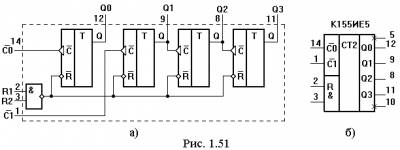

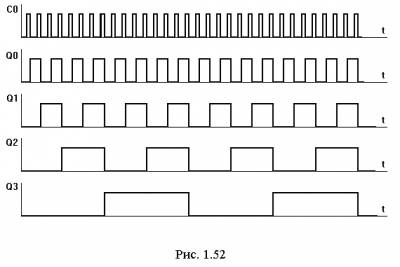

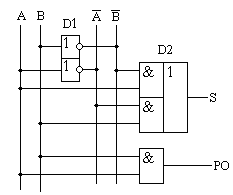

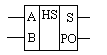

Счетчики электрических импульсов имеются как в ТТЛ, так и в КМОП сериях. В качестве примера счетчика ТТЛ рассмотрим микросхему К155ИЕ5. Функциональная схема счетчика К155ИЕ5 приведена на рисунке 1.51,а, а его условное обозначение на принципиальных схемах на рисунке 1.51,б. Счетчик К155ИЕ5 имеет фактически два счетчика: с коэффициентом пересчета два (вход С0 и выход Q0) и с коэффициентом пересчета восемь (вход С1 и выходы Q1, Q2, Q3). Счетчик с коэффициентом пересчета шестнадцать легко получается, если соединить выход Q0 с входом С1, а импульсы подавать на вход С0. Временная диаграмма работы такого счетчика приведена на рисунке 1.52.

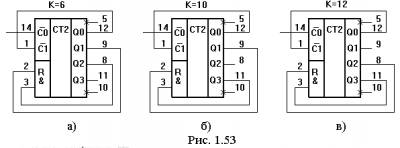

На рисунке 1.53 приведены схемы подключения, изменяющие коэффициент пересчета счетчика К155ИЕ5. Выходы счетчика Q0, Q1, Q2, Q3 имеют соответственно весовые коэффициенты 1, 2, 4, 8. Соединив выходы Q1, Q2 с входами установки счетчика в нуль, получим счетчик с коэффициентом пересчета шесть (рис. 1.53,а). На рисунке 1.53,б показана схема подключения для получения коэффициента пересчета десять, а на рисунке 1.53,в – двенадцать. Однако в схемах, приведенных на рисунках 1.53,а – в, отсутствует возможность установки счетчиков в нулевое состояние.

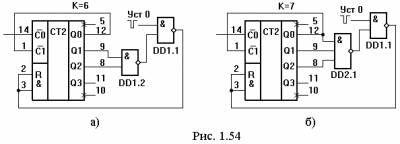

На рисунках 1.54,а, б приведены соответственно счетчики с коэффициентами пересчета шесть и семь, в которых предусмотрен вход установки счетчика в нулевое состояние. Анализ работы схем, приведенных на рисунках 1.53 – 1.54, показывает, что для получения заданного коэффициента пересчета соединяют с входами логического элемента И те выходы счетчика, весовые коэффициенты которых в сумме дают необходимый коэффициент пересчета.

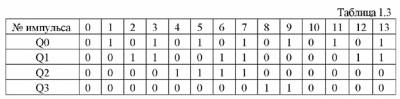

В таблице1.3 приведены состояния на выходах счетчика с коэффициентом пересчета десять после поступления каждого очередного импульса, причем счетчик предварительно был установлен в нулевое состояние.

|

| |

| |

| SlaVe4U | Дата: Среда, 12.01.2011, 03:22 | Сообщение # 35 |

|

Главный Администратор

Группа: Администраторы

Сообщений: 320

Награды: 23

Репутация: 222

Статус: Offline

|

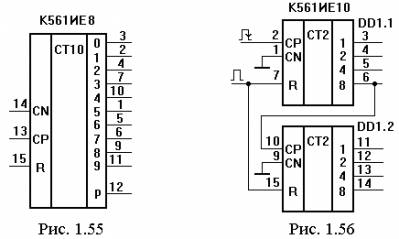

Рассмотрим некоторые из счетчиков КМОП серии. На рисунке 1.55 приведено условное обозначение микросхемы К561ИЕ8 – десятичного счетчика с дешифратором. Микросхема имеет вход установки в нулевое состояние R, вход для подачи счетных импульсов положительной полярности CP и вход для подачи счетных импульсов отрицательной полярности CN.

Переключение счетчика происходит по спадам импульсов положительной полярности на входе CP, при этом на входе CN должна быть логическая единица. Переключение счетчика будет происходить по спадам импульсов отрицательной полярности на входе CN, если на входеCP логический нуль. На одном из десяти выходов счетчика всегда присутствует логическая единица. Установка счетчика в нуль происходит при подаче на вход R логической единицы. При установке счетчика в нулевое состояние на выходе «0» установится логическая единица, а на всех остальных выходах – логические нули. Микросхемы К561ИЕ8 можно объединять в многоразрядные счетчики с последовательным переносом, соединяя выход переноса предыдущей микросхемы с входом CN последующей. На рисунке 1.56 приведена схема многоразрядного счетчика на микросхемах К561ИЕ10.

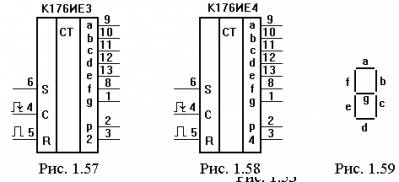

Промышленностью выпускаются счетчики для электронных часов. Рассмотрим некоторые из них. На рисунке 1.57 приведено условное обозначение микросхемы К176ИЕ3, а на рисунке 1.58 – микросхемы К176ИЕ4. На этих рисунках выходы микросхем показаны для стандартного обозначения сегментов индикатора, приведенного на рисунке 1.59. Эти микросхемы отличаются друг от друга коэффициентом пересчета. Коэффициент пересчета микросхемы К176ИЕ3 равен шести, а коэффициент пересчета микросхемы К176ИЕ4 равен десяти. Установка в нуль рассматриваемых счетчиков осуществляется подачей сигнала логической единицы на вход R. Переключение триггеров счетчика происходит по спаду положительных импульсов на входе С. Микросхемы имеют выход переноса р (вывод 2), к которому подключается обычно вход следующего счетчика. Спад напряжения на этом выходе формируется в момент перехода счетчика из состояния 9 в состояние 0. Микросхемы различаются сигналами на выводе 3. Для микросхемы К176ИЕ3 на выводе 3 появляется логическая единица при установке счетчика в состояние 2, а для микросхемы К176ИЕ4 – в состояние 4. Это необходимо для обнуления показаний часов в 24 часа.

При подаче сигнала логического нуля на вход S логические единицы на выходах счетчика будут на тех сегментах, которые отображают число импульсов, поступивших на вход счетчика. При подаче на вход S логической единицы полярность выходных сигналов изменяется. Возможность переключения полярности выходных сигналов позволяет достаточно просто изменить схему подключения цифровых индикаторов.

|

| |

| |

| SlaVe4U | Дата: Среда, 12.01.2011, 03:23 | Сообщение # 36 |

|

Главный Администратор

Группа: Администраторы

Сообщений: 320

Награды: 23

Репутация: 222

Статус: Offline

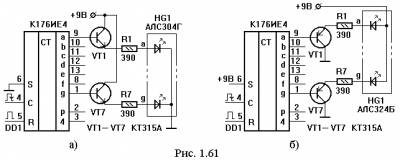

| На рисунке 1.60 приведена схема подключения люминесцентного индикатора к выходам микросхемы К176ИЕ4. Подключение индикатора к выходам микросхемы К176ИЕ3 будет аналогичным.

Схемы подключения светодиодных индикаторов к выходам микросхемы 176ИЕ4 приведены на рисунках 1.61,а и 1.61,б. На входе Sустанавливается логический нуль для индикаторов с общим катодом и логическая единица для индикаторов с общим анодом.

Описание микросхем К176ИЕ5, К176ИЕ12, К176ИЕ13, К176ИЕ17, К176ИЕ18, К176ИД2, К176ИД3 и их применение в электронных часах можно найти в [29]. Микросхемы К176ИЕ12, К176ИЕ13, К176ИЕ17, К176ИЕ18 допускают напряжение питания от 3 до 15 В.

Универсальные счетчики могут работать в режимах сложения, вычитания, установки начального кода, установки счетчика в нуль. К универсальным счетчикам относятся К155ИЕ6, К155ИЕ7, К561ИЕ11, К561ИЕ14. Алгоритм работы счетчика К155ИЕ6 рассматривается во второй главе.

|

| |

| |

| SlaVe4U | Дата: Среда, 12.01.2011, 03:25 | Сообщение # 37 |

|

Главный Администратор

Группа: Администраторы

Сообщений: 320

Награды: 23

Репутация: 222

Статус: Offline

| Билет № 32

Смотреть Билет № 34

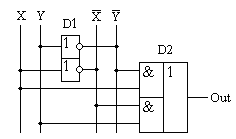

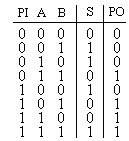

$IMAGE1$

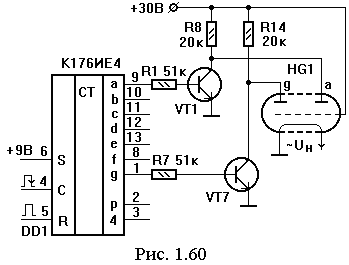

Распределитель импульсов (электронный коммутатор) представляет собой счетчик, осуществляющий деление входных импульсов в соответствии с числом каналов усилителя мощности. Требования, предъявляемые к распределителю, можно сформулировать следующим образом:

Распределение импульсов по заданному числу каналов в произвольной комбинации при минимальном количестве элементов; надежная работа в широком диапазоне частот, включая и нулевую; обеспечение реверса с любого импульса без пропуска информации. Наиболее полно указанным требованиям соответствуют транзисторные распределители. Следует отметить, что принцип построения распределителя и элементы, из которых он выполнен, при сохранении числа тактов коммутации не оказывают влияния на выходные характеристики шагового привода.

Выбор основных элементов и варианта распределителя определяется только удобствами согласования его с выходным усилителем, простотой и надежностью схемы. Управление нереверсивным распределителем импульсов осуществляется по одному каналу. Для осуществления реверса ШД необходимо изменять последовательность переключения каналов распределителя и соответственно обмоток ШД, что достигается одним из следующих способов.

В схемах с двумя перекрестными связями и двумя входами наличие импульсов на одном из входов соответствует прямой последовательности переключения, а на другом - обратной. В схемах, где управление реверсивным распределителем производится по одному каналу разнополярными импульсами, реверс ШД осуществляется при изменении полярности входных импульсов. Если управление распределителем осуществляется по одному каналу однополярными импульсами, то изменение направления вращения производится с помощью триггера реверса.

Для управления триггером требуется один канал при разнополярных импульсах или два канала, если используются однополярные импульсы. Наибольшее распространение нашел первый способ реверсирования, отличающийся высокой помехозащищенностью и универсальностью. Второй способ удобно использовать при ограниченном количестве каналов управления. Третий способ реверса имеет наибольшее количество каналов управления и минимальную помехозащищенность, так как потеря информации в канале реверса (или появление импульсной помехи) приведет к неправильной отработке всей серии входных импульсов.

Число каналов распределителя и последовательность их переключения определяются количеством фаз ШД. Он состоит из четырех однотипных ячеек, каждая из которых содержит: транзистор типа П26, нагрузочное сопротивление сопротивление "внешней" связи, линию задержки, диод "внутренней" связи и элементы запуска. осуществляющие логическую операцию И. Для обеспечения надежного запирания база транзистора связана через сопротивление с источником смещения.

Внутренние связи выполнены таким образом, что в открытом состоянии находятся одновременно два транзистора. Импульс, поступающий на любой из входов, проходит на два транзистора, подтверждая состояние одного и открывая другой. И усилителю мощности: Рассмотренная схема является частным случаем m-фазного унифицированного распределителя. Принцип, положенный в основу этих схем, позволяет создать распределители с любым числом тактов коммутации.

Он представляет собой трехстабильный триггер с емкостной коммутацией. Импульсные трансформаторы совместно с диодами и сопротивлениями нагрузки образуют схемы совпадения. Задержка напряжения обратной связи, снимаемого с сопротивления нагрузки, обеспечивается перезарядом коммутирующего конденсатора. Поэтому длительность входного импульса не должна быть больше времени восстановления управляющих свойств тиристора.

При подаче напряжения питания схема устанавливается в исходное состояние за счет заряда конденсатора. Как и в предыдущей схеме, импульс, поданный на любой из входов, поступает на два тиристора, подтверждая состояние одного и включая другой. Импульсы, поступающие на Вход обеспечивают переключение тиристоров в последовательности 1-2-3-1, а на Вход 2- в последовательности 1-3-2-1. Рассмотренная схема может быть использована для непосредственного управления ШД, если нагрузочные сопротивления 100 ом заменить обмотками управления. Принципиальная схема трехтактного тиристорного распределителя.

Усилители мощности: Коммутация обмоток управления ШД производится усилителями мощности. Принцип их построения и типы коммутирующих элементов оказывают значительное влияние на характеристики шагового привода. Шаговый двигатель является разновидностью синхронного с частотным регулированием. Следовательно, для полного использования ШД во всем диапазоне частот и улучшения его энергетических показателей необходимо регулировать величину питающего напряжения. При этом существенно усложняется система привода, снижается ее надежность и увеличивается инерционность регулирования.

|

| |

| |

| SlaVe4U | Дата: Среда, 12.01.2011, 03:26 | Сообщение # 38 |

|

Главный Администратор

Группа: Администраторы

Сообщений: 320

Награды: 23

Репутация: 222

Статус: Offline

| 35

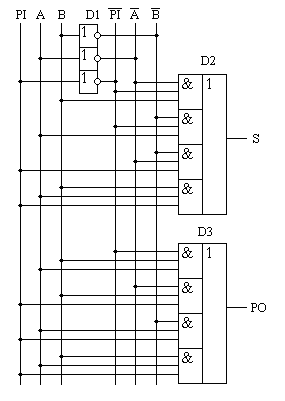

Мультиплексор - это устройство, которое осуществляет выборку одного из нескольких входов и подключает его к своему выходу, в зависимости от состояния двоичного кода. Другими словами, мультиплексор - переключатель сигналов, управляемый двоичным кодом и имеющий несколько входов и один выход. К выходу подключается тот вход, чей номер соответствует двоичному коду. Ну и навороченное определение: мультиплексор - это устройство, преобразующее параллельный код в последовательный.

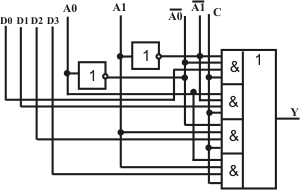

Структуру мультиплексора можно представить различными схемами, но более понятна, на мой взгляд, вот эта:

Рис. 1 - Структура мультиплексора

Самая большая хренотень есть не что иное, как элемент И-ИЛИ. Конкретно здесь элемент 4-х входовый. Ну а квадратики с единичками внутри, если кто не помнит, инверторы. Разберем выводы. Те, что слева, а именно D0-D3, называются информационными входами. На них чего-нибудь подают. Входы посередке, а именно А0-А1, называются адресными входами. Вот сюда именно и подается двоичный код, от которого зависит, какой из входов D0-D3 будет подключен к выходу, на этой схеме обозначенному как Y. Вход С, черт его знает, нафига он здесь. Вроде бы как разрешение работы, а может просто для понта. Ну его в баню. На схеме еще есть входы адреса с инверсией. Так вот они тоже показаны здесь для понта. На этом рисунке показан четырехвходовой, или как еще его называют, 4Х1 мультиплексор. Потому и адресных входов всего 2. Как нам известно, максимальное число переменных определяется как 2n, где n - разряд кода. Здесь мы видим, что переменных четыре штуки, а значит разряд будет равен 2 (22 = 4). Для пояснения принципа работы этой схемы посмотрим на табличку истинности:

A1 A0 Y

0 0 D0

0 1 D1

1 0 D2

1 1 D3

Вот так двоичный код выбирает нужный вход. Т. е., если имеем четыре объекта, ну, скажем, они пуляют сигналы, а устройство отображения у нас одно. Берем мультик (мультиплексор) и втуляем его в схему. В зависимости от двоичного кода к устройству отображения подключается сигнал от нужного объекта. Такой вот, дохленький пример.

Микросхемой мультик обозначается вот так:

Вообще, мультиплексоров всяких дофига. Есть и сдвоенные четырехвходовые, восьмивходовые, 16-ти входовые, счетверенные двухвходовые и пр. Тот, что на рисунке сделан от фонаря.

Демультиплексор. Демультиплексор - устройство, обратное мультиплексору. Т. е., у демультиплексора один вход и куча выходов. Двоичный код определяет, какой выход будет подключен ко входу. Другими словами, демультиплексор - это устройство, которое осуществляет выборку одного из нескольких выходов и подключает его к своему входу или, это переключатель сигналов, управляемый двоичным кодом и имеющий один вход и несколько выходов. Ко входу подключается тот выход, чей номер соответствует состоянию двоичного кода. И навороченное определение: демультиплексор - это устройство, которое преобразует последовательный код в параллельный.

Обычно в качестве демультиплексора используют дешифраторы двоичного кода в позиционный, в которых вводят дополнительный вход стробирования. Из-за схожести структур мультиплексора и демультиплексора в КМОП сериях есть микросхемы, которые одновременно являются мультиплексорром и демультиплексором, смотря с какой стороны подавать сигналы, например, К561КП1, работающая как переключатель 8х1 и переключатель 1х8 (то бишь, как мультиплексор и демультиплексор с восемью входами или выходами). Кроме того, в КМОП микросхемах помимо переключения цифровых сигналов (лог. 0 или 1) существует возможность переключения аналоговых. Другими словами, это переключатель аналоговых сигналов, управляемый цифровым кодом. Такие микросхемы называются коммутаторами. К примеру, с помощью коммутатора можно переключать сигналы, поступающие на вход усилителя (селектор входов). Вот напоследок простенькую схемку селектора входов УМЗЧ мы и рассмотрим. Построим ее, ну скажем, с использованием триггеров и мультиплексора.

|

| |

| |

| SlaVe4U | Дата: Среда, 12.01.2011, 03:27 | Сообщение # 39 |

|

Главный Администратор

Группа: Администраторы

Сообщений: 320

Награды: 23

Репутация: 222

Статус: Offline

|

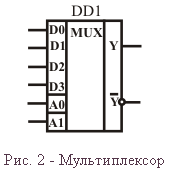

Рис. 3 - Селектор входных сигналов

Вот такая нехитрая схемка. Итак, разберем работу и деталюшки. На триггерах микросхемы DD1 собран кольцевой счетчик нажатий кнопки разрядностью 2 (два триггера - 2 разряда). Двухразрядный двоичный код поступает на адресные входы D0-D1 микросхемы DD2. Микросхема DD2 представляет собой сдвоенный четырехканальный коммутатор. В соответствии с двоичным кодом к выходам микросхемы А и В подключаются входы А0-А3 и В0-В3 соответственно. Элементы R1, R2, C1 устраняют дребезг контактов кнопки.Дифференцирующая цепь R3C2 устанавливает триггеры в нулевое состояние при включении питания, при этом к выходу подключается первый вход. При нажатии на кнопку триггер DD1.1 переключается в состояние лог. 1 и к выходу подключается второй вход и т. д. Перебор входов идет по кольцу, начиная с первого.

С одной стороны просто, с другой немного неудобно. Черт его знает, сколько раз нажали на кнопку после включения и какой вход подключен к выходу. Хорошо бы поставить индикатор подключенного входа. Вот тут-то и пригодится семисегментный дешифратор. Нажимаем ссылочку, вспоминаем семисегментный дешифратор и смотрим на схемку (там, где циферки бегут). Берем дешифратор и индикатор, обрубаем счетчик и другую галиматью, переносим дешифратор с индикатором на схему коммутатора и первые два входа дешифратора (на схеме обозначен как DD3), т. е. 1 и 2 (выв. 7 и 1) подключаем к прямым выходам триггеров DD1.1 DD1.2 (выв. 1 и 13). Входы дешифратора 4 и 8 (выв. 2 и 6) кидаем на корпус (т. е. подаем лог. 0). Все! Индикатор будет показывать состояние кольцевого счетчика, а именно циферки от 0 до 3. Цифиря 0 соответствует первому входу, 1 - 2-му и т. д.

|

| |

| |

| SlaVe4U | Дата: Среда, 12.01.2011, 03:27 | Сообщение # 40 |

|

Главный Администратор

Группа: Администраторы

Сообщений: 320

Награды: 23

Репутация: 222

Статус: Offline

| 36

Цифровой компаратор

Цифровой компаратор или компаратор амплитуд является электронным устройством берущим два числа в двоичном виде и определяющим является ли первое число меньшим, большим или равным второму числу.

Компараторы используются в центральных процессорах и микроконтроллерах. Примерами цифровых компараторов являются КМОП — 4063 и 4585, ТТЛ — 7485 и 74682-89.

Аналоговым эквивалентом цифрового компаратора является компаратор напряжений. Некоторые микроконтроллеры имеют аналоговые компараторы на некоторых своих входах, которые могут быть считаны или включать прерывание.

Действие однобитного цифрового компаратора может быть выражено таблицей истинности:

Входы Выходы

A B A < B A = B A > B

0 0 0 1 0

0 1 1 0 0

1 0 0 0 1

1 1 0 1 0

Действие двухцифрового компаратора может быть выражено таблицей истиности:

Входы Выходы

A1 A0 B1 B0 A < B A = B A > B

0 0 0 0 0 1 0

0 0 0 1 1 0 0

0 0 1 0 1 0 0

0 0 1 1 1 0 0

0 1 0 0 0 0 1

0 1 0 1 0 1 0

0 1 1 0 1 0 0

0 1 1 1 1 0 0

1 0 0 0 0 0 1

1 0 0 1 0 0 1

1 0 1 0 0 1 0

1 0 1 1 1 0 0

1 1 0 0 0 0 1

1 1 0 1 0 0 1

1 1 1 0 0 0 1

1 1 1 1 0 1 0 Рассмотрим два 4-х битных числа A и B

A = A3A2A1A0

B = B3B2B1B0

Здесь каждая буква с цифрой представляет одну из цифр в числе.

Равенство (эквивалентность)

Двоичные числа A и B будут равны, если все пары значащих цифр обоих чисел равны, т.е.,

A3 = B3, A2 = B2, A1 = B1 и A0 = B0

Так как числа являются двоичными, то цифры являются или 0 или 1. Булева функция для равенства любых двух цифр Ai и Bi может быть выражена как

.

xi равна 1 только если Ai и Bi равны.

Для равенства A и B, все функции xi (для i=0,1,2,3) должны быть равны 1.

Состояние равенства A и B может быть выражено используя операции И, как

Двоичная функция (A=B) равна 1 только если все пары цифр двух чисел равны.

Неравенство (неэквивалентность)

Чтобы определить наибольшее из двух двоичных чисел, мы рассмотрим отношение величин пар значащих цифр, начиная с наиболее значащих битов, последовательно продвигаясь к младшим значащим битам до нахождения неравенства. Когда неравенство найдено, то, если соответствующий бит A равен 1 и такой же бит B равен 0, то мы считаем, что A>B.

Это последовательное сравнение может быть выражено логически как:

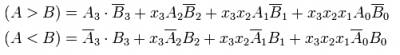

|

| |

| |

| SlaVe4U | Дата: Среда, 12.01.2011, 03:29 | Сообщение # 41 |

|

Главный Администратор

Группа: Администраторы

Сообщений: 320

Награды: 23

Репутация: 222

Статус: Offline

|

(A>B) и (A <  - выходные двоичные переменные, которые равны 1 когда A>B или A<B соответственно. - выходные двоичные переменные, которые равны 1 когда A>B или A<B соответственно. Цифровые компараторы (от английского compare — сравнивать) выполняют сравнение двух чисел А, В одинаковой разрядности, заданных в двоичном или двоично-десятичном коде. В зависимости от схемного исполнения компараторы могут определять равенство А=В или неравенства А<В, А>В. Результат сравнения отображается в виде логического сигнала на одноименных выходах.

Цифровые компараторы применяются для выявления нужного числа (слова) в цифровых последовательностях, для отметки времени в часовых приборах, для выполнения условных переходов в вычислительных устройствах, а также в адресных селекторах [18].

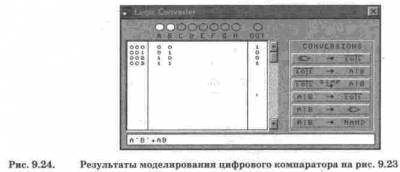

Схема одноразрядного компаратора приведена на рис. 9.23. Компаратор состоит из двух элементов НЕ, четырех элементов И и одного элемента ИЛИ-НЕ.

Для исследования компаратора к нему подключен логический преобразователь. Подсоединяя его клемму OUT к каждому выходу компаратора, можно получить таблицу истинности и булево выражение для каждого режима работы компаратора. Для случая А=В, показанного на рис. 9.23, результаты моделирования представлены на рис. 9.24, откуда видно, что условию А=В соответствуют две комбинации сигналов на входе: А=В=1 или А=В=0. Этому условию и отвечает булево выражение на дополнительном дисплее.

Устройство контроля четности

Операция контроля четности двоичных чисел позволяет повысить надежность передачи и обработки информации. Ее сущность заключается в суммировании по модулю 2 всех разрядов с целью выяснения четности числа, что позволяет выявить наиболее вероятную ошибку в одном из разрядов двоичной последовательности. Например, если при передаче кода 1001 произойдет сбой во втором разряде, то на приемном пункте получим код 1101 — такую ошибку определить в общем случае затруднительно. Если же код относится к двоично-десятичному (8-4-2-1), то ошибку легко обнаружить, поскольку полученный код (десятичный эквивалент — число 13) не может в принципе принадлежать к двоично-десятичному.

Обнаружение ошибок путем введения дополнительного бита четности происходит следующим образом. На передающей стороне передаваемый код анализируется и дополняется контрольным битом до четного или нечетного числа единиц в суммарном коде. Соответственно суммарный код называется четным или нечетным. В случае нечетного кода дополнительный бит формируется таким образом, чтобы сумма всех единиц в передаваемом коде, включая контрольный бит, была нечетной. При контроле четности все, естественно, наоборот. Например, в числе 0111 число единиц нечетно. Поэтому при контроле нечетности дополнительный бит должен быть нулем, а при контроле четности — единицей. На практике чаще всего используется контроль нечетности, поскольку он позволяет фиксировать полное пропадание информации (случай нулевого кода во всех информационных разрядах). На приемной стороне производится проверка кода четности. Если он правильный, то прием разрешается, в противном случае включается сигнализация ошибки или посылается передатчику запрос на повторную передачу.

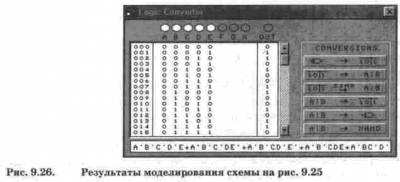

Схема формирования бита четности [8] для четырехразрядного кода показана на рис. 9.25. Она содержит четыре элемента Исключающее ИЛИ, выполняющих функции сумматоров по модулю 2 (без переноса) и состоит из трех ступеней. На первой ступени попарно суммируются все биты исходного кода на входах А, В, С, D. На второй ступени анализируются сигналы первой ступени и устанавливается четность или нечетность суммы входного кода. На третьей ступени полученный результат сравнивается с контрольным сигналом на входе Е, задающим вид используемого контроля, в результате чего на выходе F формируется пятый дополнительный бит четности, сопровождающий информационный сигнал в канале передачи.

|

| |

| |

| SlaVe4U | Дата: Среда, 12.01.2011, 03:30 | Сообщение # 42 |

|

Главный Администратор

Группа: Администраторы

Сообщений: 320

Награды: 23

Репутация: 222

Статус: Offline

|

Результаты моделирования формирователя показаны на рис. 9.26 в виде таблицы истинности из 32 возможных двоичных комбинаций и булева выражения (из 32 комбинаций на рис. 9.26 видны только первые 16, остальные просматриваются с помощью линейки прокрутки). Для просмотра составляющих булева выражения необходимо мышью поместить курсор в дополнительный дисплей и передвигать его клавишами управления курсором.

В библиотеке программы EWB схема проверки на четность и нечетность представлена ИМС 74280 (аналог — К555ИП5), схема ее включения показана на рис. 9.27. ИМС 74280 имеет 9 входов (A, B...I) и два выхода (EVEN, ODD), один из которых — инверсный. Вход I используется для управления видом контроля (0 — контроль четности, 1 — контроль нечетности) и управляется переключателем Z (управляется с клавиатуры одноименной клавишей). Вывод NC — not connection — пустой, т.е. внутри ИМС к нему ничего не подключено.

Правильность функционирования схемы на рис. 9.27 проверяется с помощью генератора слова, при этом тип контроля (четности или нечетности) выбирается переключателем Z; на входы рассматриваемого устройства подаются различные двоичные комбинации; состояние выходов ИМС контролируется подключенными к ним светоиндикаторами (логическими пробниками).

|

| |

| |

| SlaVe4U | Дата: Среда, 12.01.2011, 03:30 | Сообщение # 43 |

|

Главный Администратор

Группа: Администраторы

Сообщений: 320

Награды: 23

Репутация: 222

Статус: Offline

| 37

СМотреть

|

| |

| |

| SlaVe4U | Дата: Среда, 12.01.2011, 03:32 | Сообщение # 44 |

|

Главный Администратор

Группа: Администраторы

Сообщений: 320

Награды: 23

Репутация: 222

Статус: Offline

| 38

Построение двоичных сумматоров обычно начинается с сумматора по модулю 2. На рисунке 1 приведена таблица истинности этого сумматора. Ее можно получить исходя из правил суммирования в двоичной арифметике. Предполагается, что читатель знаком с основами двоичной арифметики. Более подробно операции над двоичными числами будут рассмотрены позднее.

Рисунок 1. Таблица истинности сумматора по модулю 2.

В соответствии с принципами построения произвольной таблицы истинности, рассмотренными в предыдущей главе, получим схему сумматора по модулю 2. Эта схема приведена на рисунке 2.

Рисунок 2. Принципиальная схема, реализующая таблицу истинности сумматора по модулю 2.

Сумматор по модулю 2 (для двоичной арифметики его схема совпадает со схемой исключающего "ИЛИ") изображается на схемах как показано на рисунке 3.

Рисунок 3. Изображение схемы, выполняющей логическую функцию исключающего "ИЛИ".

Сумматор по модулю 2 выполняет суммирование без учета переноса. В полном двоичном сумматоре требуется учитывать перенос, поэтому требуются схемы, позволяющие формировать перенос в следующий двоичный разряд. Таблица истинности такой схемы, называемой полусумматором, приведена на рисунке 4.

Рисунок 4. Таблица истинности полусумматора.

В соответствии с принципами построения произвольной таблицы истинности получим схему полусумматора. Эта схема приведена на рисунке 5.

Полусумматор изображается на схемах как показано на рисунке 6.

Рисунок 6. Изображение полусумматора на схемах.

Схема полусумматора формирует перенос в следующий разряд, но не может учитывать перенос из предыдущего разряда, поэтому она и называется полусумматором. Таблицу истинности полного двоичного одноразрядного сумматора можно получить из правил суммирования двоичных чисел. Она приведена на рисунке 7. В обозначении входов использовано следующее правило: в качестве входов использованы одноразрядные числа A и B; перенос обозначен буквой P; для обозначения входа переноса используется буква I (сокращение от английского слова input – вход); для обозначения выхода переноса используется буква O (сокращение от английского слова output – выход).

|

| |

| |

| SlaVe4U | Дата: Среда, 12.01.2011, 03:34 | Сообщение # 45 |

|

Главный Администратор

Группа: Администраторы

Сообщений: 320

Награды: 23

Репутация: 222

Статус: Offline

|

Рисунок 7. Таблица истинности полного двоичного одноразрядного сумматора.

В соответствии с принципами построения принципиальной схемы по произвольной таблице истинности получим схему полного двоичного одноразрядного сумматора. Эта схема приведена на рисунке 8. Ее можно минимизировать, но это несколько усложняет принципы построения сумматоров, поэтому вопросы минимизации рассматриваться не будут.

Рисунок 8. Принципиальная схема, реализующая таблицу истинности полного двоичного одноразрядного сумматора.

Полный двоичный одноразрядный сумматор изображается на схемах как показано на рисунке 9.

Рисунок 9 Изображение полного двоичного одноразрядного сумматора на схемах.

Для того чтобы получить многоразрядный сумматор, достаточно соединить входы и выходы переносов соответствующих двоичных разрядов. Схема соединения одноразрядных сумматоров для реализации четырехразрядного сумматора приведена на рисунке 10.

|

| |

| |

|