|

Электротехника

| |

| SlaVe4U | Дата: Среда, 12.01.2011, 02:53 | Сообщение # 16 |

|

Главный Администратор

Группа: Администраторы

Сообщений: 320

Награды: 23

Репутация: 222

Статус: Offline

| 12. Нетактируемые Е-, R-, S- триггеры в сравнении с RS- триггером.

НИХЕРА НЕТ 13. Нетактируемый и тактируемый потенциалом D-триггеры.

АНАЛОГИЧНО 14. Двухтактный тактируемый фронтом D-триггер.

Триггеры

Триггер - это устройство последовательного типа с двумя устойчивыми состояниями равновесия, предназначенное для записи и хранения информации. Под действием входных сигналов триггер может переключаться из одного устойчивого состояния в другое. При этом напряжение на его выходе скачкообразно изменяется. Как правило, триггер имеет два выхода: прямой и инверсный. Число входов зависит от структуры и функций, выполняемых триггером. По способу записи информации триггеры делят на асинхронные и синхронизируемые (тактируемые). В асинхронных триггерах информация может записываться непрерывно и определяется информационными сигналами, действующими на входах в данный момент времени. Если информация заносится в триггер только в момент действия так называемого синхронизирующего сигнала, то такой триггер называют синхронизируемым или тактируемым. Помимо информационных входов тактируемые триггеры имеют тактовый вход вход синхронизации. В цифровой технике приняты следующие обозначения входов триггеров:

S - раздельный вход установки в единичное состояние (напряжение высокого уровня на прямом выходе Q);

R - раздельный вход установки в нулевое состояние (напряжение низкого уровня на прямом выходе Q);

D - информационный вход (на него подается информация, предназначенная для занесения в триггер);

C - вход синхронизации;

Т - счетный вход. Наибольшее распространение в цифровых устройствах получили RS-триггер с двумя установочными входами, тактируемый D-триггер и счетный Т-триггер. Рассмотрим функциональные возможности каждого из них.

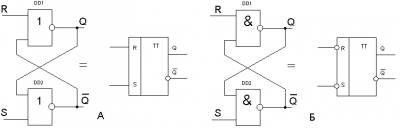

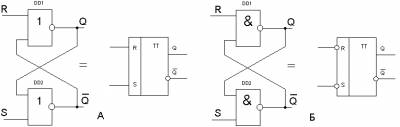

Асинхронный RS-трнггер. В зависимости от логической структуры различают RS-триггеры с прямыми и инверсными входами. Их схемы и условные обозначения приведены на рисунке. Триггеры такого типа построены на двух логических элементах 2ИЛИ-НЕ - триггер с прямыми входами (а), 2И-НЕ - триггер с инверсными входами (б).

Выход каждого из элементов подключен к одному из выходов другого элемента. Здесь приведены таблицы истинности для каждого из этих триггеров

S R Qt -Qt Qt+1 -Qt+1 S R Qt -Qt Qt+1 -Qt+1

0 1 0 1 0 1 0 1 0 1 1 0

1 0 0 1 1 0 1 0 0 1 0 1

0 0 0 1 0 1 0 0 0 1 * *

1 1 0 1 * * 1 1 0 1 0 1

0 1 1 0 0 1 0 1 1 0 1 0

1 0 1 0 1 0 1 0 1 0 0 1

0 0 1 0 1 0 0 0 1 0 * *

1 1 1 0 * * 1 1 1 0 0 1 В таблицах (Qt и -Qt обозначают уровни, которые были на выходах триггера до подачи на его входы так называемых активных уровней. Активным. называют логический уровень, действующий на входе логического элемента и однозначно определяющий логический уровень выходного сигнала (независима от логических уровней, действующих на остальных входах). Для элементов ИЛИ-НЕ за активный уровень принимают высокий уровень, а для элементов И-НЕ - низкий уровень. Уровни, подача которых на один из входов не приводит к изменению логического уровня на выходе элемента, называют пассивными. Уровни Qt+1 и -Qt+1 обозначают логические уровни на выходах Триггера после подачи информации на его входы. Для триггера с прямыми входами Qt+1=1 при S=1 и R=0; Qt+1=0 при S=0 и R=1; Qt+1= Qt при S=0 и R=0. При R=S=1 состояние триггера будет неопределенным, так как во время действия информационных сигналов Логические уровни на выходах триггера одинаковы (Qt+1=-Qt+1=0), а после окончания их действия триггер может равновероятно принять любое из устойчивых состояний. Поэтому такая комбинация является запрещенной (и может вывести триггер из строя). Режим S=1, R=0 называют режимом записи 1 (так как Qt+1=1); режим S=0 и R=1 - режимом записи 0. Режим S=0, R=О называется режимом хранения информации, так как информация на выходе остается неизменной. Для триггера с инверсными входами режим записи логической 1 реализуется при -S=0, -R=1, режим записи логического 0 - при -S=1, -R=0. При -S=-R=1 обеспечивается хранение информации. Комбинация S=R=0 является запрещенной.

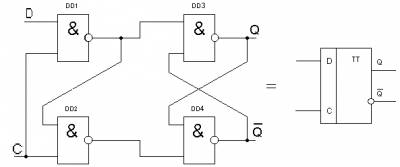

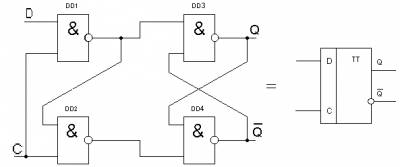

Следует, однако, отметить, что самостоятельно RS-триггеры в устройствах цифровой техники практически не используются из-за их низкой помехоустойчивости Тактируемый D-триггер. Он имеет информационный выход и вход синхронизации. Одна из возможных структурных схем однотактного D-триггера и его условное обозначение показаны на рисунке.

|

| |

| |

| SlaVe4U | Дата: Среда, 12.01.2011, 02:54 | Сообщение # 17 |

|

Главный Администратор

Группа: Администраторы

Сообщений: 320

Награды: 23

Репутация: 222

Статус: Offline

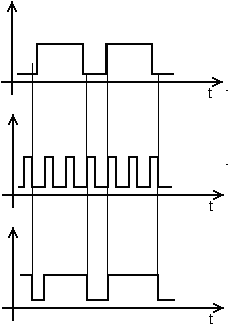

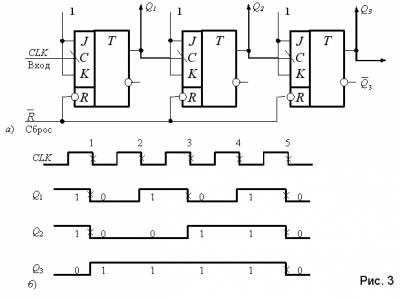

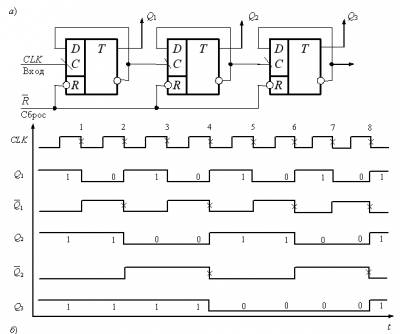

| Если уровень сигнала на входе C= 0, состояние триггера устойчиво и не зависит от уровня сигнала на информационном входе. При этом на входы RS-триггера с инверсными входами (элементы 3 и 4) поступают пассивные уровни (-S=-R=1). При подаче на вход синхронизации уровня С=1 информация на прямом выходе будет повторять информацию, подаваемую на вход D. Таким образом, при C=0 Qt+1=Qt, C=1 Qt+1=D). Таблица истинности тактируемого D-трнггера имеет вид: D C Qt+1 0 0 0 0 1 0 1 0 1 1 1 1 Здесь Qt означает логический уровень на прямом выходе до подачи импульса синхронизации, а Qt+1 - логический уровень на этом выходе после подачи импульса синхронизации. На рисунке 3 изображены временные диаграммы тактируемого D-триггера. В таком триггере происходит задержка сигнала на выходе по отношению к сигналу, поданному на вход. на время паузы между синхросигналами. Для устойчивой работы триггера необходимо, чтобы в течение синхроимпульса информация на входе была неизменной.

Тактируемые D-триггеры могут быть с потенциальным и динамическим управлением. У первых из них информация записывается в течение времени, при котором уровень сигнала С=1. В триггерах с динамическим управлением информация записывается только в течение перепада напряжения на входе синхронизации. Динамические входы изображают на схемах треугольником. Если вершина треугольника обращена в сторону микросхемы, то триггер срабатывает по фронту входного импульса, если от нее - по срезу. Еще в схемах вы встретите / и \ обозначения первое соответственно фронт второе спад. В таком триггере информация на входе может быть задержана на один такт по отношению к входной информации.

Счетный Т-триггер рисунок 4,а. Его называют также триггером со счетным входом. Он имеет один управляющий вход Т и два выхода Q и -Q. Информация на выходе такого триггера меняет свой знак на противоположный при каждом положительном (или при каждом отрицательном) перепаде напряжения на входе. Триггер такого типа может быть создан на базе тактируемого D-триггера, если его инверсный выход соединить с информационным входом (рис 4,б). Как видно из диаграммы на Рисунке 4,в, частота сигнала на выходе Т-триггера в два раза ниже частоты сигнала на входе, поэтому такой триггер можно использовать как делитель частоты и двоичный счетчик. В сериях выпускаемых микросхем есть также универсальные JK-триггеры. При соответствующем подключении входной логики JK-триггер может выполнить функции триггера любого другого типа.

|

| |

| |

| SlaVe4U | Дата: Среда, 12.01.2011, 02:55 | Сообщение # 18 |

|

Главный Администратор

Группа: Администраторы

Сообщений: 320

Награды: 23

Репутация: 222

Статус: Offline

| 15.Тактируемый фронтом D-триггер, выполненный на шести ячейках И-НЕ, типа ТМ-2 (ТТЛ).

Триггеры

Триггер - это устройство последовательного типа с двумя устойчивыми состояниями равновесия, предназначенное для записи и хранения информации. Под действием входных сигналов триггер может переключаться из одного устойчивого состояния в другое. При этом напряжение на его выходе скачкообразно изменяется. Как правило, триггер имеет два выхода: прямой и инверсный. Число входов зависит от структуры и функций, выполняемых триггером. По способу записи информации триггеры делят на асинхронные и синхронизируемые (тактируемые). В асинхронных триггерах информация может записываться непрерывно и определяется информационными сигналами, действующими на входах в данный момент времени. Если информация заносится в триггер только в момент действия так называемого синхронизирующего сигнала, то такой триггер называют синхронизируемым или тактируемым. Помимо информационных входов тактируемые триггеры имеют тактовый вход вход синхронизации. В цифровой технике приняты следующие обозначения входов триггеров:

S - раздельный вход установки в единичное состояние (напряжение высокого уровня на прямом выходе Q);

R - раздельный вход установки в нулевое состояние (напряжение низкого уровня на прямом выходе Q);

D - информационный вход (на него подается информация, предназначенная для занесения в триггер);

C - вход синхронизации;

Т - счетный вход. Наибольшее распространение в цифровых устройствах получили RS-триггер с двумя установочными входами, тактируемый D-триггер и счетный Т-триггер. Рассмотрим функциональные возможности каждого из них.

Асинхронный RS-трнггер. В зависимости от логической структуры различают RS-триггеры с прямыми и инверсными входами. Их схемы и условные обозначения приведены на рисунке. Триггеры такого типа построены на двух логических элементах 2ИЛИ-НЕ - триггер с прямыми входами (а), 2И-НЕ - триггер с инверсными входами (б).

Выход каждого из элементов подключен к одному из выходов другого элемента. Здесь приведены таблицы истинности для каждого из этих триггеров

S R Qt -Qt Qt+1 -Qt+1 S R Qt -Qt Qt+1 -Qt+1

0 1 0 1 0 1 0 1 0 1 1 0

1 0 0 1 1 0 1 0 0 1 0 1

0 0 0 1 0 1 0 0 0 1 * *

1 1 0 1 * * 1 1 0 1 0 1

0 1 1 0 0 1 0 1 1 0 1 0

1 0 1 0 1 0 1 0 1 0 0 1

0 0 1 0 1 0 0 0 1 0 * *

1 1 1 0 * * 1 1 1 0 0 1 В таблицах (Qt и -Qt обозначают уровни, которые были на выходах триггера до подачи на его входы так называемых активных уровней. Активным. называют логический уровень, действующий на входе логического элемента и однозначно определяющий логический уровень выходного сигнала (независима от логических уровней, действующих на остальных входах). Для элементов ИЛИ-НЕ за активный уровень принимают высокий уровень, а для элементов И-НЕ - низкий уровень. Уровни, подача которых на один из входов не приводит к изменению логического уровня на выходе элемента, называют пассивными. Уровни Qt+1 и -Qt+1 обозначают логические уровни на выходах Триггера после подачи информации на его входы. Для триггера с прямыми входами Qt+1=1 при S=1 и R=0; Qt+1=0 при S=0 и R=1; Qt+1= Qt при S=0 и R=0. При R=S=1 состояние триггера будет неопределенным, так как во время действия информационных сигналов Логические уровни на выходах триггера одинаковы (Qt+1=-Qt+1=0), а после окончания их действия триггер может равновероятно принять любое из устойчивых состояний. Поэтому такая комбинация является запрещенной (и может вывести триггер из строя). Режим S=1, R=0 называют режимом записи 1 (так как Qt+1=1); режим S=0 и R=1 - режимом записи 0. Режим S=0, R=О называется режимом хранения информации, так как информация на выходе остается неизменной. Для триггера с инверсными входами режим записи логической 1 реализуется при -S=0, -R=1, режим записи логического 0 - при -S=1, -R=0. При -S=-R=1 обеспечивается хранение информации. Комбинация S=R=0 является запрещенной.

Следует, однако, отметить, что самостоятельно RS-триггеры в устройствах цифровой техники практически не используются из-за их низкой помехоустойчивости Тактируемый D-триггер. Он имеет информационный выход и вход синхронизации. Одна из возможных структурных схем однотактного D-триггера и его условное обозначение показаны на рисунке.

|

| |

| |

| SlaVe4U | Дата: Среда, 12.01.2011, 02:56 | Сообщение # 19 |

|

Главный Администратор

Группа: Администраторы

Сообщений: 320

Награды: 23

Репутация: 222

Статус: Offline

| Если уровень сигнала на входе C= 0, состояние триггера устойчиво и не зависит от уровня сигнала на информационном входе. При этом на входы RS-триггера с инверсными входами (элементы 3 и 4) поступают пассивные уровни (-S=-R=1). При подаче на вход синхронизации уровня С=1 информация на прямом выходе будет повторять информацию, подаваемую на вход D. Таким образом, при C=0 Qt+1=Qt, C=1 Qt+1=D). Таблица истинности тактируемого D-трнггера имеет вид: D C Qt+1 0 0 0 0 1 0 1 0 1 1 1 1 Здесь Qt означает логический уровень на прямом выходе до подачи импульса синхронизации, а Qt+1 - логический уровень на этом выходе после подачи импульса синхронизации. На рисунке 3 изображены временные диаграммы тактируемого D-триггера. В таком триггере происходит задержка сигнала на выходе по отношению к сигналу, поданному на вход. на время паузы между синхросигналами. Для устойчивой работы триггера необходимо, чтобы в течение синхроимпульса информация на входе была неизменной.

Тактируемые D-триггеры могут быть с потенциальным и динамическим управлением. У первых из них информация записывается в течение времени, при котором уровень сигнала С=1. В триггерах с динамическим управлением информация записывается только в течение перепада напряжения на входе синхронизации. Динамические входы изображают на схемах треугольником. Если вершина треугольника обращена в сторону микросхемы, то триггер срабатывает по фронту входного импульса, если от нее - по срезу. Еще в схемах вы встретите / и \ обозначения первое соответственно фронт второе спад. В таком триггере информация на входе может быть задержана на один такт по отношению к входной информации.

Счетный Т-триггер рисунок 4,а. Его называют также триггером со счетным входом. Он имеет один управляющий вход Т и два выхода Q и -Q. Информация на выходе такого триггера меняет свой знак на противоположный при каждом положительном (или при каждом отрицательном) перепаде напряжения на входе. Триггер такого типа может быть создан на базе тактируемого D-триггера, если его инверсный выход соединить с информационным входом (рис 4,б). Как видно из диаграммы на Рисунке 4,в, частота сигнала на выходе Т-триггера в два раза ниже частоты сигнала на входе, поэтому такой триггер можно использовать как делитель частоты и двоичный счетчик. В сериях выпускаемых микросхем есть также универсальные JK-триггеры. При соответствующем подключении входной логики JK-триггер может выполнить функции триггера любого другого типа.

|

| |

| |

| SlaVe4U | Дата: Среда, 12.01.2011, 02:58 | Сообщение # 20 |

|

Главный Администратор

Группа: Администраторы

Сообщений: 320

Награды: 23

Репутация: 222

Статус: Offline

| 16. Счетный Т-триггер.

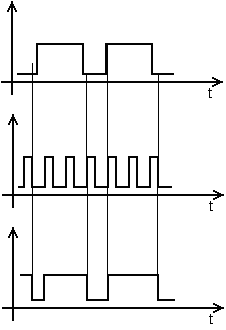

Т-триггер - это счетный триггер. Т-триггер имеет один вход (вспомогательные входы принудительной установки “0” и “1” не рассматриваются), куда подают тактирующие (счетные ) импульсы. После подачи каждого тактирующего импульса состояние Т-триггера меняется в обратное (инверсное) предыдущему состоянию (аналогично состоянию JK-триггера при комбинации входных переменных J=1 и K=1). Т-триггеры строятся только на базе двухступенчатых (RS, D, JK) триггеров. Т-триггер можно синтезировать из любого типа двухступенчатого триггера. Рассмотрим пример синтеза Т-триггера из JK-триггера. Для этого Т-триггер представим как совокупность комбинационного устройства КУ и JK-триггера (рис. 3.19).

Приведенное на рис.3.19, (а) комбинационное устройство должно обеспечить на выходах J и K соответствующие сигналы управления RS-триггером (при подаче на его входы сигналов Q и Т), в соответ-ствии с таблицей состояний (рис. 3.19, б). Карты Карно, с помощью которых получены минимальные формы логических выражений для функций J и K, приведены на рис 3.20.

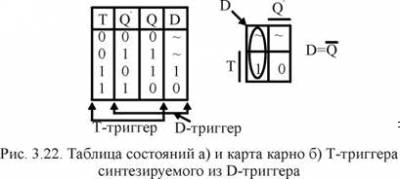

Счетный триггер можно синтезировать и на базе D-тригера. Рассмотрим пример реализации Т-триггера на базе D-триггера, управляемого фронтом синхроимпульса. Совмещенная таблица состояний синтезируемого триггера и D-триггера приведена на рис. 3.22, (а). Карта Карно, используемая для минимизации логического выражения функции, КУ, содержит всего один контур с двумя клетками и, следовательно, функция будет содержать тоже всего одну переменную (рис. 3.22, б).

Из логического выражения функции D следует, что для получения счетного триггера из D-триггера, достаточно соединить инверсный выход D-триггера с его входом “D” (рис. 3.23).

Временные диаграммы, поясняющие принцип работы счетного триггера приведены на рис. 3.24. Из временных диаграмм следует, что переключение состояния счетного триггера, выполненного на базе D-триггера, происходит в моменты поступления передних фронтов синхроимпульсов. Частота следования импульсов на выходе счетного триггера в два раза меньше частоты входных синхроимпульсов, что позволяет их использовать в качестве делителей частоты. Если один счетный триггер позволяет делить частоту на два, то для реализации делителя частоты на четыре потребуется два триггера, соединенных последовательно и т.д.

|

| |

| |

| SlaVe4U | Дата: Среда, 12.01.2011, 02:58 | Сообщение # 21 |

|

Главный Администратор

Группа: Администраторы

Сообщений: 320

Награды: 23

Репутация: 222

Статус: Offline

| 17. Тактируемый IK - триггер.

18. Нетактируемый IK-триггер. 19. Регистры памяти и оперативные запоминающие устройства.

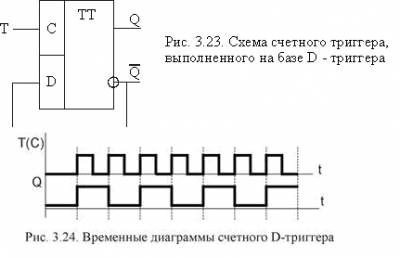

Регистры памяти - простейший вид регистров . Их назначение хранить двоичную информацию небольшого объема в течение короткого промежутка времени. Эти регистры представляют собой набор синхронных триггеров , каждый из которых хранит один разряд двоичного числа. Ввод (запись, загрузка) и вывод (считывание) информации производится одновременно во всех разрядах параллельным кодом. Запись обеспечивается тактовым импульсом. С приходом очередного тактового импульса происходит обновление записанной информации. Сигналы на выходах триггеров характеризуют выходную информацию. Считывание может производиться в прямом или в обратном коде (в последнем случае - с инверсных выходов). Регистры памяти (хранения) представляют собой , по существу, наборы триггеров с независимыми информационными входами и (обычно) общим тактовым входом. В качестве регистров подобного рода могут быть использованы без дополнительных элементов многие типы синхронных триггеров. Особенно пригодны микросхемы, содержащие в одном корпусе несколько самостоятельных триггеров, например: К155ТМ8, К155ТМ5, К155ТМ7, К155ТМ8 и др., которые можно рассматривать как четырехразрядные регистры памяти. На рис.1 приведена функциональная схема ИМС К155ТМ8, которая содержит четыре D-триггера с динамическим управлением. Микросхема имеет 4 раздельных информационных входа, прямые и инверсные выходы Q и Q от каждого триггера и общие для всех триггеров выходы синхронизации и установки нулей (сброса). Запись данных, поступивших на информационные входы, происходит одновременно во всех триггерах по фронту 0,1 сигнала на входе С , при этом на входе R должен быть высокий уровень (логическая 1). Установка триггеров в нулевое состояние выполняется сигналом НИЗКОГО уровня (лог. 0) на входе R. При использовании микросхемы К155ТМ8 в качестве четырехразрядного регистра памяти она изображается как на рис.2.

|

| |

| |

| SlaVe4U | Дата: Среда, 12.01.2011, 03:00 | Сообщение # 22 |

|

Главный Администратор

Группа: Администраторы

Сообщений: 320

Награды: 23

Репутация: 222

Статус: Offline

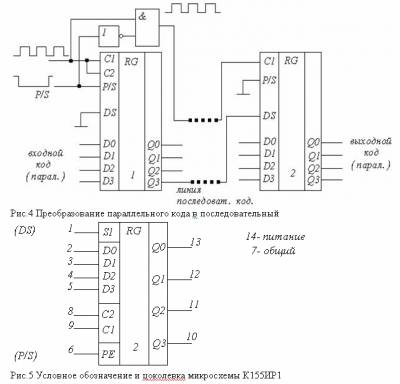

| 20. Регистры сдвига.

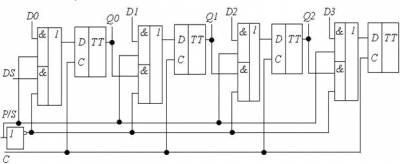

Кроме операции хранения данных регистры могут использоваться и для операции сдвига данных с целью преобразования двоичного последовательного кода в параллельный и наоборот. Это так называемые сдвиговые регистры или регистры сдвига, которые получаются путем цепочного соединения триггеров. Суть сдвига состоит в том, что по сигналу синхроимпульса происходит одновременная перезапись содержимого каждого триггера в соседний триггер. При этом не меняется само двоичное слово (число), записанное в регистре, оно лишь сдвигается на один разряд и только содержимое последнего триггера ТТ3 пропадает из регистра, а на вход первого ТТ0 поступает новый бит(см. рис.1)

а) б) Рис. 1. Сдвигающий регистр а) схема на непрозрачных триггерах б) условное обозначение Сдвигающий регистр в отличие от регистра памяти должен обязательно состоять из непрозрачных триггеров, иначе при первом же сигнале сдвига бит, поступивший на вход первого триггера регистра сдвига, сразу же пройдёт на выход этого триггера и соответственно, на вход второго триггера, а значит и на выход второго триггера и т. д. до последнего триггера регистра сдвига. В некоторых сдвиговых регистрах сдвиг происходит не только в одну сторону, а и влево и вправо - это так называемые реверсивные регистры. Чтобы обеспечить реверс сдвига и параллельную запись сразу во все триггеры к D-входу каждого i-того триггера подключён мультиплексор, который при подаче " 1 " на один из управляющих входов - SL(Shift Left - сдвиг влево), SR(Shift Right - сдвиг вправо) или PL(Parallel load - параллельная загрузка) подключает вход i-того триггера соответственно к выходу младшего соседа (направление A), старшего соседа (направление  или к выходу параллельной загрузки Di (см. рис.2). Точка A самого младшего триггера (разряда) является входом DR, точка В самого старшего разряда - входом DL (входы DL и DR используются для наращивания разрядности реверсивных регистров). Выход i-го триггера подключён к соответствующим входам мультиплексоров соседних разрядов. По С-сигналу триггеры регистра принимают информацию с направлений, диктуемых мультиплексорами. или к выходу параллельной загрузки Di (см. рис.2). Точка A самого младшего триггера (разряда) является входом DR, точка В самого старшего разряда - входом DL (входы DL и DR используются для наращивания разрядности реверсивных регистров). Выход i-го триггера подключён к соответствующим входам мультиплексоров соседних разрядов. По С-сигналу триггеры регистра принимают информацию с направлений, диктуемых мультиплексорами.

Рис.2 Схема одного разряда реверсивного регистра. На рис.3 представлена принципиальная схема сдвигового регистра с параллельным и последовательным вводом данных.

Рис.3 Сдвиговый регистр с возможностью параллельного и последовательного ввода данных. DS - Data Serial - вход для последовательного ввода данных P/S - Parallel/Serial - выбор режима работы Чтобы 4-х разрядное двоичное число, представленное в параллельном коде, преобразовать в последовательный код, надо сначала разряды этого числа подать на входы D0,D1,D2,D3 регистра, а одновременно с этим подать разрешение на параллельную запись, т.е. P/S = 1 и подать один или несколько импульсов на С-вход регистра. После этого нужно запретить параллельную запись в регистр и тем самым разрешить последовательный режим регистра (P/S = 0). Теперь на каждый синхроимпульс выход D3 будет выдавать поочерёдно разряды записанного двоичного числа. Обычно последовательный код начинается младшим разрядом, а в данном регистре первым на выход поступит разряд числа, записанный ранее на триггер ТТ3, значит при параллельной записи следует проследить, чтобы младший разряд был записан в триггер ТТ3, а старший - в ТТ0. Рассмотрим схему преобразования параллельного кода в последовательный, приведённую на рис.4. Данные параллельным кодом загружаются в регистр RG1, пока P/S=1. Затем при P/S=0 RG1 переходит в режим сдвига (последовательный режим) и в течение 4-х импульсов на С- входе RG1 содержимое этого регистра с его выхода Q3 разряд за разрядом передаётся на RG2 на вход DS, где записывается последовательным кодом благодаря подаче 4-х синхроимпульсов на вход C RD2. После этого данные могут быть считаны параллельным кодом с выходов Q0-Q3 регистра RG2.

|

| |

| |

| SlaVe4U | Дата: Среда, 12.01.2011, 03:02 | Сообщение # 23 |

|

Главный Администратор

Группа: Администраторы

Сообщений: 320

Награды: 23

Репутация: 222

Статус: Offline

| 21. Регистр последовательного приближения.

22. Кольцевые счетчики импульсов.

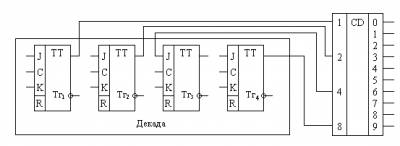

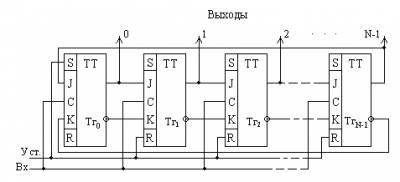

В рассмотренных выше счетчиках число поступлений на вход импульсов представляется в форме двоичного числа, цифры разрядов которого выражаются через состояние триггеров. При этом, если требуется получить десятичное представление числа импульсов, к выходам счетчика подключается дешифратор. На рис. 52 показано подключение дешифратора к декаде десятичного счетчика. В этой схеме уровень лог. 1 появляется на том из выходов дешифратора, десятичный номер которого соответствует двоичному числу в счетчике. В процессе счета с каждым поступлением на вход импульса происходит переход лог. 1 на следующий выход, номер которого на единицу больше. Неудобства, связанные с необходимостью применения дешифратора, устраняются в кольцевом счетчике. В нем число поступлений импульсов выражается непосредственно в десятичной системе счисления и не возникает необходимости в использовании дешифратора.

рис 8.52 Кольцевой счетчик строится в виде сдвигового регистра, в котором выдвигаемая из старшего разряда информация вводится в младший разряд. Схема счетчика показана на рис. 8.53. В счетчике использовано N триггеров. Перед началом счета импульсом начальной установки триггер Тг0 устанавливается в состояние 1, остальные триггеры - в состояние 0. Этому состоянию счетчика соответствует число О; на выход счетчика, обозначенный цифровой 0, с прямого выхода триггера Тг0 передается лог. 1. Далее каждый из приходящих на вход счетчика импульсов переписывает 1 в следующий триггер и лог. 1 передается на следующий выход, обозначенный цифрой, на единицу большей. Таким образом, по тому, какой из триггеров находится в состоянии 1, т. е. на выходе какого из триггеров возникает уровень лог. 1, выявляется число поступивших на

рис 8.53 вход счетчика импульсов непосредственно в десятичной системе счисления. Кольцевой счетчик обеспечивает высокую скорость работы. Это связано с тем, что единица из одного триггера в другой передается непосредственно (без использования в цепи передачи логических элементов) путем подключения входов J и К каждого триггера соответственно к прямому и инверсному выходам предыдущего триггера. После подачи N - 1 импульсов в состоянии 1 окажется триггер ТгN-1 а с приходом N-го импульса единица из триггера ТгN-1 перепишется в триггер Тг0 и счет импульсов начнется сначала. Таким образом, период цикла кольцевого счетчика равен числу использованных в нем триггеров. Например, для построения декады десятичного счетчика по принципу кольцевого счетчика потребуется 10 триггеров (вместо четырех триггеров в двоичном счетчике). Таким образом, возможность получения из счетчика чисел непосредственно в десятичной системе счисления достигается существенным увеличением числа используемых в схеме счетчика элементов.

|

| |

| |

| SlaVe4U | Дата: Среда, 12.01.2011, 03:04 | Сообщение # 24 |

|

Главный Администратор

Группа: Администраторы

Сообщений: 320

Награды: 23

Репутация: 222

Статус: Offline

| 23. Асинхронные двоичные счетчики импульсов с последовательным переносом.

Асинхронные счетчики строятся в виде цепочки триггеров со счетным входом (Т- вход для Т – триггера; С – вход для JK - триггера при J=K=1; C – вход для D – триггера, где D вход соединен с инверсным выходом триггера). Счетный вход каждого последующего триггера счетчика подключается к выходу или предыдущего, что зависит как от направления счета, так и от фронта тактирующего входа триггера

Асинхронный суммирующий счетчик, построенный на JK- триггерах (а) и временная диаграмма его работы (б). .

Схема суммирующего счетчика, построенная на JK - триггерах и временная диаграмма его работы приведены на рис. 3. На рис. 3 обозначение на триггере указывает на срабатывание триггера на задний фронт синхросигнала в момент времени 1, 2, 3, 4, 5 для первого счетного триггера Q1. 1, 3, 5 – для второго Q2 и 1, 5 – для третьего Q3, как показано на диаграмме рис. 3, б). Если входы C (JK- триггера) соединить с инверсными выходами предыдущих триггеров, то получится схема вычитающего счетчика. Аналогично, если в схеме вычитающего счетчика на D - триггерах (рис.4) синхронизируемые входы C триггеров соединить с прямыми выходами Q предыдущих триггеров, то счетчик станет суммирующим.

Счетчики на рис. 3 и 4 называют последовательными, так как в них каждый триггер переключается выходным сигналом предыдущего. Эти счетчики отличаются простой схемой, но недостатком является из низкое быстродействие в режиме регистрации входных сигналов, так как в этом режиме нельзя подавать очередной входной сигнал, пока не зафиксировано предыдущее состояние счетчика. Время установления кода равно tуст = nt зд. тр, где t зд. тр - время задержки переключения триггера. Очевидно, что максимальная частота входных сигналов в режиме регистрации составляет fмакс.рег=1/tуст. Впрочем, в режиме деления входной последовательности импульсов максимальная частота их поступления на младший разряд счетчика будет ограничиваться быстродействием младшего триггера и составит fмакс.дел=1/tзд.тр.

Рис. 4. Асинхронный вычитающий счетчик на D- триггерах (а) и временная диаграмма его работы (б). Другой недостаток последовательных счетчиков заключается в том, что из-за последовательного переключения триггеров, в счетчике возникает на короткие промежутки времени много других состояний. Поэтому если к выходам такого счетчика подключить дешифратор, то на выходах дешифратора могут появиться короткие ложные сигналы, соответствующие промежуточным фазам перехода счетчика из одного состояния в другое.

Для устранения этих недостатков используют синхронные счетчики.

|

| |

| |

| SlaVe4U | Дата: Среда, 12.01.2011, 03:04 | Сообщение # 25 |

|

Главный Администратор

Группа: Администраторы

Сообщений: 320

Награды: 23

Репутация: 222

Статус: Offline

| 24. Синхронные двоичные счетчики импульсов со сквозным и параллельным переносом.

25. Двоичные реверсивные счетчики импульсов.

26. Асинхронные двоично-десятичные счетчики импульсов.

Асинхронный двоичный счетчик

Асинхронный двоичный счетчик может быть реализован в виде цепочки триггеров ( как показано на рис. 20.3), тактовый вход каждого из которых подключен к выходу Q предыдущего триггера. Для получения суммирующего счетчика триггеры должны изменять свое состояние при переходе тактового сигнала из 1 в О.

Микросхема представляет собой асинхронный двоичный счетчик с предварительной установкой.

Микросхема представляет собой четырехразрядный асинхронный двоичный счетчик.

Однако построение асинхронных двоичных счетчиков на J / C-триггерах в ряде случаев нерационально, так как счетчики на У / С-триггерах по сравнению со счетчиками на D-триггерах имеют большие аппаратурные затраты и меньшее быстродействие.

Основой микросхемы является 12-разрядный асинхронный двоичный счетчик, который отсчитывает / V входных импульсов от своего начального состояния до заполнения ( состояние - все 1) и вырабатывает командный импульс, по которому формируется выходной сигнал на выводах 8 и 9, а сам счетчик устанавливается в начальное состояние, определяемое кодом / V, содержащимся в регистре хранения коэффициента деления.

Асинхронный двоичный счетчик с последовательными переносами на. На рис. 7.25 показан четырехразрядный асинхронный двоичный счетчик, реализованный на JK-триггерах. На входы J и К каждого триггера поданы единичные сигналы. Выход каждого триггера i - ro разряда соединен с входом синхронизации следующего ( j l) - ro разряда. Состояние каждого разряда изменяется на отрицательном перепаде, следовательно, для триггера нулевого разряда изменение происходит на отрицательном фронте хсч, а для триггеров остальных разрядов - при возникновении сигналов переноса на предыдущих триггерах. Отметим, что распространение этих сигналов переноса происходит последовательно от разряда к разряду. Это ограничивает быстродействие из-за того, что времена распространения сигналов при их прохождении через счетчик последовательно суммируются и при увеличении числа разрядов накопленная задержка может привести к сбою в работе.

Реверсивный регистр сдвига.| Асинхронный двоичный счетчик. В этом заключается недостаток асинхронного двоичного счетчика.

Асинхронные двоично-десятичные счетчики на / Л - триггерах выполняются на основе асинхронных двоичных счетчиков. 27. Двоично-десятичный счетчик импульсов, работающий в невзвешен-ном коде.

|

| |

| |

| SlaVe4U | Дата: Среда, 12.01.2011, 03:05 | Сообщение # 26 |

|

Главный Администратор

Группа: Администраторы

Сообщений: 320

Награды: 23

Репутация: 222

Статус: Offline

| 28

Двоичные счетчики: Схему двоичного счетчика можно получить с помощью формального синтеза, однако более наглядным путем представляется эвристический. Таблица истинности двоичного счетчика — последовательность двоичных чисел от нуля до 2n − 1, где n - разрядность счётчика. Наблюдение за разрядами чисел, составляющих таблицу, приводит к пониманию структурной схемы двоичного счетчика. Состояния младшего разряда при его просмотре по соответствующему столбцу таблицы показывают чередование нулей и единиц вида 01010101..., что естественно, т. к. младший разряд принимает входной сигнал и переключается от каждого входного воздействия. В следующем разряде наблюдается последовательность пар нулей и единиц вида 00110011... . В третьем разряде образуется последовательность из четверок нулей и единиц 00001111... и т.д. Из этого наблюдения видно, что следующий по старшинству разряд переключается с частотой, в два раза меньшей, чем данный. Известно, что счетный триггер делит частоту входных импульсов на два. , Сопоставив этот факт с указанной выше закономерностью, видим, что счетчик может быть, построен в виде цепочки последовательно включенных счетных триггеров. Заметим, кстати, что согласно ГОСТу входы элементов изображаются слева, а выходы справа. Соблюдение этого правила ведет к тому, что в числе, содержащемся в счетчике, младшие разряды расположены левее старших.

Счётчик числа импульсов — устройство, на выходах которого получается двоичный(двоично-десятичный) код, определяемый числом поступивших импульсов. Счётчики могут строиться на T-триггерах. Основной параметр счётчика — модуль счёта — максимальное число единичных сигналов, которое может быть сосчитано счётчиком. Счётчики обозначают через СТ (от англ. counter).

Счётчики классифицируют:

по числу устойчивых состояний триггеров

на двоичных триггерах

на троичных триггерах

на n-ичных триггерах

по модулю счёта:

двоично-десятичные (декада);

двоичные;

с произвольным постоянным модулем счёта;

с переменным модулем счёта;

по направлению счёта:

суммирующие;

вычитающие;

реверсивные;

по способу формирования внутренних связей:

с последовательным переносом;

с параллельным переносом;

с комбинированным переносом;

кольцевые;

по способу переключения триггера:

синхронные;

асинхронные;

Счётчик Джонсона

В состав рассматриваемых серий ТТЛ-микросхем входит большое число счетчиков и делителей частоты, различающихся по своим свойствам и назначению.

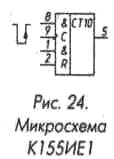

Микросхема К155ИЕ1 (рис. 24) - делитель частоты на 10. Установка триггеров микросхемы в 0 осуществляется подачей лог. 1 одновременно на два объединенных по схеме И входа R. Рабочая полярность входных счетных импульсов, подаваемых на входы С, отрицательная. Импульсы можно подавать или отдельно на каждый из входов (на второй вход

должна при этом подаваться лог. 1), или одновременно на оба входа. Одновременно с каждым десятым входным импульсом на выходе формируется равный ему по длительности выходной импульс отрицательной полярности. Многокаскадные делители частоты можно строить, соединяя входы С последующих каскадов с выходами предыдущих.

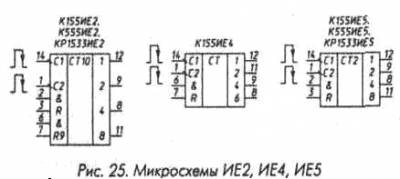

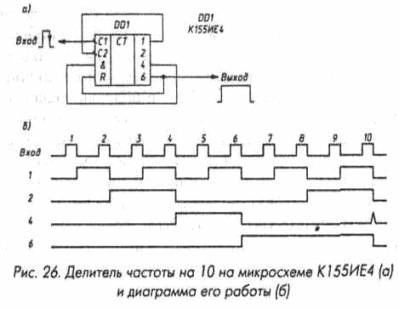

Микросхемы ИЕ2, К155ИЕ4 и ИЕ5 (рис. 25) содержат по четыре счетных триггера. В каждой микросхеме один из триггеров имеет отдельный вход С1 и прямой выход, три оставшихся триггера соединены между собой так, что образуют делитель на 8 в микросхеме ИЕ5,

на 6 в К155ИЕ4 и на 5 в ИЕ2. При соединении выхода первого триггера с входом С2 цепочки из трех триггеров образуются соответственно делители на 16, 12 и 10. Делители на 10 и 16 работают в коде 1-2-4-8, делитель на 12 - в коде 1-2-4-6. Микросхемы имеют по два входа R установки в 0, объединенные по схеме И. Сброс (установка в 0) триггеров производится при подаче лог. 1 на оба входа R. Микросхема ИЕ2 имеет, кроме того, входы R9 для установки в состояние 9, при котором первый и последний триггеры декады находятся в единичном состоянии, остальные - в нулевом.

Наличие входов установки, объединенных по схеме И, позволяет строить делители частоты с различными коэффициентами деления в пределах 2-6 без использования дополнительных логических элементов. На рис. 26 приведены схема декады на микросхеме К155ИЕ4 и ее временная диаграмма. До прихода десятого импульса декада работает как делитель частоты на 12. Десятый импульс переводит триггеры микросхемы в состояние 10, при котором на выходах 4 и 6 микросхемы формируются уровни лог. 1. Эти уровни, поступая на входы

|

| |

| |

| SlaVe4U | Дата: Среда, 12.01.2011, 03:08 | Сообщение # 27 |

|

Главный Администратор

Группа: Администраторы

Сообщений: 320

Награды: 23

Репутация: 222

Статус: Offline

| R микросхемы, переводят ее в 0, в результате чего коэффициент пересчета К становится равным 10

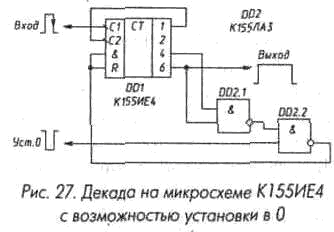

Для установки рассмотренной декады в 0 внешним сигналом необходимо введение в нее логических элементов И-НЕ (рис 27)

В табл. 4 приведены номера выводов микросхем, которые нужно соединить между собой для получения различных К Все делители, полученные соединением выводов по табл. 4, работают по одно

му принципу - при достижении состояния, соответствующего необходимому коэффициенту пересчета, происходит установка счетчика в 0. Исключение составляет делитель на 7 на микросхеме ИЕ2. В этом делителе после подсчета шести импульсов на входах R9 формируются уровни лог. 1, поэтому из состояния 5 делитель сразу переходит в состояние 9, минуя 6,7 и 8 Код работы этого делителя - невесовой

Делители на микросхемах ИЕ5 и ИЕ2 работают в весовом коде 1-2-4-8, на микросхеме К155ИЕ4 - в коде 1-2-4-6 при использовании входа 14 и в коде 1-2-3 - при использовании входа 1.

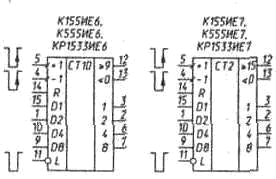

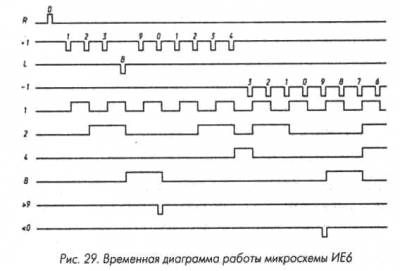

Микросхемы ИЕ6 и ИЕ7 - реверсивные счетчики. Первый из них - двоично-десятичный, второй - двоичный Оба работают в коде 1-2-4-8 Цоколевка обеих микросхем одинакова (рис 28), различие в том, что первый считает до 10, второй до 16

Рассмотрим для примера работу микросхемы ИЕ6 В отличие от рассмотренных ранее счетчиков, эта микросхема имеет большее число

Таблица 4

К К155ИЕ2 К155ИЕ4 К155ИЕ5

Вход Вых. Соединить выводы Вход Вых. Соединить выводы Вход Вых. Соединить выводы

2 14 12 14 12 - 14 12 -

3 1 8 9-2,8-3 1 9 - 1 8 9-2,8-3

4 1 8 11-2-3 1 8 11-6,8-7 1 8 -

5 1 11 - 1 8 9-6,8-7 1 11 9-2,11-3

6 14 8 12-1,9-2,8-3 1 8 - 1 11 8-2,11-3

7 14 11 12-1,9-6,8-7 14 8 12-1-6,8-7 - - -

8 14 8 12-1,11-2-3 14 8 12-1,11-6,8-7 1 11 -

9 14 11 12-1-2,11-3 - - - 14 1 1 12-1-2,11-3

10 14 11 12-1 14 8 12-1,9-6,8-7 14 11 12-1,9-2,11-3

12 - 14 8 12-1 14 11 12-1,8-2,11-3

16 - - - - - - 14 11 12-1

выходов и входов Входы +1 и -1 служат для подачи тактовых импульсов, +1 - при прямом счете, -1 - при обратном. Вход R служит для установки счетчика в 0, вход L - для предварительной записи в счетчик информации, поступающей по входам D1 - D8.

Установка триггеров счетчика в 0 происходит при подаче лог 1 на вход R, при этом на входе L должна быть лог. 1. Для предварительной записи в счетчик любого числа от 0 до 9 его код следует подать на входы D1 - D8 (D1 - младший разряд, D8 - старший), при этом на входе R должен быть лог 0, и на вход L подать импульс отрицательной полярности

Режим предварительной записи можно использовать для построения делителей частоты с перестраиваемым коэффициентом деления для учета фиксированной частоты (например, 465 кГц) в цифровой шкале радиоприемника Если этот режим не используется, на выходе L должен постоянно поддерживаться уровень лог 1

Прямой счет осуществляется при подаче импульсов отрицательной полярности на вход +1, при этом на входах -1 и L должна быть лог 1, на входе R - лог 0 Переключение триггеров счетчика происходит по спадам входных импульсов, одновременно с каждым десятым входным импульсом на выходе >=9 формируется отрицательный выходной импульс переполнения, который может подаваться на вход +1 следующей микросхемы многоразрядного счетчика Уровни на выходах 1-2-4-8 счетчика соответствуют состоянию счетчика в данный момент (в двоичном коде) При обратном счете входные импульсы подаются на вход -1, выходные импульсы снимаются с выхода <=0 Пример временной диаграммы работы счетчика приведен на рис. 29.

Первый импульс установки в 0 устанавливает все триггеры счетчика в 0. Три следующих импульса, поступающих на вход +1, переводят счетчик в состояние 3, которому соответствуют лог. 1 на выходах 1 и 2 и лог 0 - на 4 и 8. Если на входах D1 - D4 лог. 0, на входе D8 лог. 1, импульс на входе L устанавливает счетчик в состояние 8 Следующие

шесть импульсов, поступающие на вход +1, переводят счетчик последовательно в состояния 9,0,1,2,3,4 Одновременно с импульсом, переводящим счетчик в 0, на выходе S9 появляется выходной импульс прямого счета Следующие импульсы, поступающие на вход -1, изменяют состояние счетчика в обратном порядке 3, 2, 1,0,9,8 и т д

|

| |

| |

| SlaVe4U | Дата: Среда, 12.01.2011, 03:11 | Сообщение # 28 |

|

Главный Администратор

Группа: Администраторы

Сообщений: 320

Награды: 23

Репутация: 222

Статус: Offline

| Одновременно с импульсом обратного счета, переводящим счетчик в состояние 9, на выходе <=0 появляется выходной импульс.

В микросхеме ИЕ7 импульс на выходе =>15 появляется одновременно с импульсом на входе +1 при переходе счетчика из состояния 15 в состояние 0, а на выходе <=0 - при переходе счетчика из 0 в 15 одновременно с импульсом на входе -1.

Предельная частота функционирования микросхем К155ИЕ6, К155ИЕ7 - 15 МГц, К555ИЕ6 и К555ИЕ7 - 25 МГц, КР1533ИЕ6 и КР1533ИЕ7 - 30 МГц.

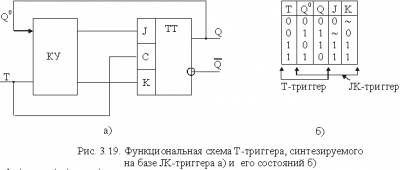

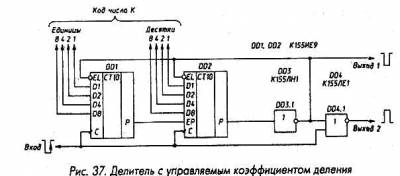

Микросхему К155ИЕ8 обычно называют делителем частоты с переменным коэффициентом деления, однако это не совсем точно. Эта микросхема содержит шестиразрядный двоичный счетчик, элементы совпадения, позволяющие выделять не совпадающие между собой импульсы - каждый второй, каждый четвертый, каждый восьмой и т. д. и управляемый элемент И-ИЛИ, который позволяет подавать на выход часть или все выделенные импульсы, в результате чего сред-

$IMAGE1$

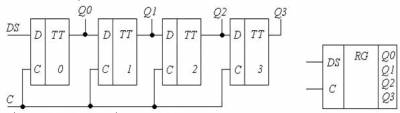

няя частота выходных импульсов может изменяться от 1/64 до 63/64 частоты входных импульсов. Графическое обозначение микросхемы приведено на рис. 30, пример временной диаграммы ее работы - на рис. 31. Для наглядности на рис. 30 вынесен логический элемент И-НЕ, входящий в микросхему. Микросхема имеет следующие входы: инверсный вход ЕС - разрешения

$IMAGE2$

счета, при подаче на который лог. 1 счетчик не считает, вход R - установки 0, установка триггеров счетчика в 0 происходит при подаче на него лог. 1; вход С - вход тактовых импульсов отрицательной полярности, переключение триггеров счетчика происходит по спадам входных импульсов; входы XI - Х32 позволяют управлять выдачей отрицательных выходных импульсов, совпадающих по времени с входными, на выход Z. На рис. 31 в качестве примера показано, какие импульсы выделяются на выходе Z при подаче лог. 1 на входы:

Х32 (диаграмма Х32), Х16 (диаграмма Х16) и Х8 (диаграмма Х8). В этих случаях на выходе Z выделяется соответственно 32, 16 или 8 равномерно расположенных импульсов. Если же одновременно подать лог. 1 на несколько входов, например, на Х32 и Х8, то, как показано на диаграмме Z, на выходе Z выделится 40 импульсов, но расположенных неравномерно. В общем случае число импульсов N на выходе Z за период счета составит

N = 32 х Х32 + 16 х Х16 + 8 х Х8 + 4 х Х4 + 2 х Х2 + X1, где X1-Х32 принимают значения соответственно 1 или 0 в зависимости от того, подана или нет лог. 1 на соответствующий вход.

На выходе Р выделяется отрицательный импульс, фронт которого совпадает со спадом 63-го тактового импульса, спад - со спадом 64-го. Этот импульс может использоваться при каскадном соединении интегральных микросхем К155ИЕ8. Вход S - вход стробирования, при подаче на него лог. 1 выдача импульсов на выходе Z прекращается.

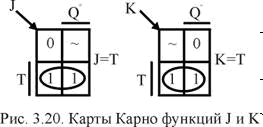

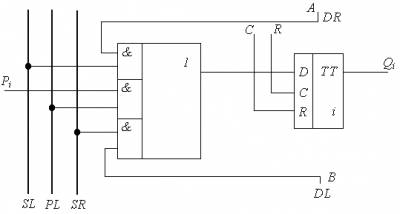

На рис. 32 приведена схема соединения двух делителей К155ИЕ8, позволяющая получить на выходе от 1 до 4095 импульсов при подаче на вход 4096 =64^2 импульсов. Число импульсов на выходе подсчитывается по формуле, аналогичной приведенной выше, в которой коэффициенты имеют значения от 2048 до 1. Если требуется соединить большее число делителей, их соединение производится аналогично рис. 32, однако выходной элемент И-НЕ, выполняющий функцию ИЛИ-НЕ

$IMAGE3$

для отрицательных импульсов, поступающих с выходов Z делителей, необходимо использовать из отдельной микросхемы И-НЕ или И.

$IMAGE4$

|

| |

| |

| SlaVe4U | Дата: Среда, 12.01.2011, 03:12 | Сообщение # 29 |

|

Главный Администратор

Группа: Администраторы

Сообщений: 320

Награды: 23

Репутация: 222

Статус: Offline

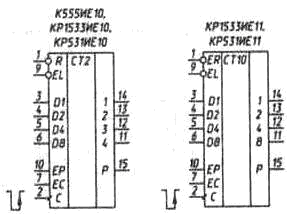

| Микросхема ИЕ9 (рис. 33) - синхронный десятичный счетчик с возможностью параллельной записи информации по фронту тактового импульса, имеет девять входов. Подача лог. 0 на вход R независимо от состояния других входов приводит к установке триггеров микросхемы в состояние 0. Для обеспечения режима счета на входе R необходимо подать лог. 1, тот же сигнал должен быть подан на входы разрешения параллельной записи EL, разрешения ЕС, разрешения выдачи сигнала переноса ER Изменение состояния триггеров счетчика при счете происходит по спаду импульсов отрицательной полярности, подаваемых на вход С.

При подаче лог. 0 на вход EL микросхема переходит в режим параллельной записи информации со входов D1 - D8. Запись происходит по спадам импульсов отрицательной полярности на входе С, что позволяет использовать микросхему в режиме сдвигающего регистра. При записи на входе R должна быть лог. 1, сигналы на входах ЕС и ЕР произвольны.

На выходе переноса Р лог. 1 появляется в том случае, когда счетчик находится в состоянии 9, а на входе ЕР - лог. 1, в остальных случаях на выходе Р лог. 0. Подача лог. 0 на вход ЕР запрещает выдачу лог. 1 на выходе Р и счет импульсов. Подача лог. 0 на вход ЕС запрещает счет, но не запрещает выдачу сигнала переноса. Сигнал запрета счета (лог. 0 на входах ЕС и ЕР) действует лишь в том случае, если он полностью перекрывает по длительности импульс отрицательной полярности на входе С, в том числе он может совпадать с ним по времени.

Для обеспечения параллельной записи лог. 0 на вход EL информация на входы D1 - D8 может быть подана как при лог. 1, так и при лог. 0 на входе С и удерживаться до момента перехода лог. 0 на входе С в лог. 1, когда и произойдет запись.

Для обеспечения счета с числа, введенного в микросхему при параллельной записи, лог 0 на входе EL должен быть изменен на лог. 1 или одновременно с переходом лог. 0 в лог. 1 на входе С, или при лог. 1 на входе С.

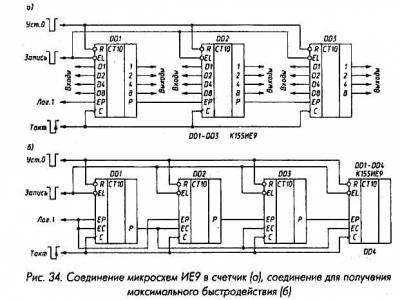

На рис. 34 (а) приведена схема соединения микросхем ИЕ9 в многоразрядный синхронный счетчик, которая снижает быстродействие счетчика, так как для его нормальной работы необходимо, чтобы сигнал переноса от младшего разряда прошел через все микросхемы до старшего разряда до подачи очередного тактового импульса. Для получения максимального быстродействия многоразрядного счетчика, равного быстродействию отдельной микросхемы, микросхемы можно соединить по схеме рис. 34 (б). В этом случае сигнал переноса с выхода Р микросхемы DD1 разрешает работу остальных микросхем, соединенных в счетчик по схеме рис. 34 (а), лишь в те моменты, когда микросхема DD1 находится в состоянии 9, поэтому от счетчика DD2 - DD9 требуется быстродействие в 10 раз меньшее быстродействия микросхемы DD1, что обеспечивается при любой практически встречающейся длине счетчика.

Как уже указывалось выше, микросхемы ИЕ9 могут работать в режиме сдвигающего регистра. Для обеспечения такого режима необходимо входы D1 - D8 соединить с выходами 1-2-4-8 в нужном порядке. Для сдвига информации на один двоичный разряд по каждому тактовому импульсу в сторону старших разрядов соединение необходимо произвести в соответствии с рис. 35 (а). Для обеспечения динамической индикации удобно сдвигать информацию сразу на один десятичный разряд, а сдвигающий регистр замыкать в кольцо. Такая возможность проиллюстрирована на рис. 36.

На рис. 36 не показаны цепи подачи импульсов и управляющих сигналов, которые могут быть выполнены в соответствии с рис. 34 (а) или 34 (б). Роль входа разрешения сдвига выполняет вход Запись. Естественно, что при соединении микросхем в соответствии с рис. 35,36 параллельная запись информации в микросхемы невозможна.

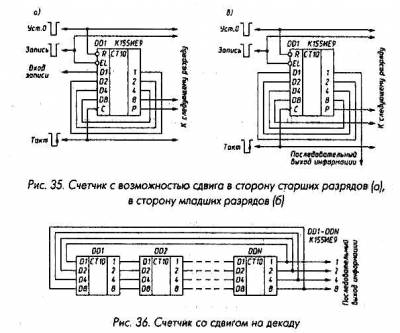

Микросхемы ИЕ9 удобно использовать в делителе с переключаемым коэффициентом пересчета. Для получения указанного режима достаточно сигнал переноса старшего разряда одноразрядного или многоразрядного счетчика через инвертор подать на вход разрешения записи, а на входы D1 - D8 подать код, определяющий коэффициент пересчета (рис. 37).

При установке счетчика в процессе счета в состояние 99...9 счетчик перейдет в режим параллельной записи и при подаче следующего тактового импульса вместо перехода в состояние 00...0 произойдет запись параллельного кода, поданного на входы D1 - D8 микросхем. В результате общий коэффициент пересчета N уменьшится на величину К, соответствующую численному значению этого кода, и составит

|

| |

| |

| SlaVe4U | Дата: Среда, 12.01.2011, 03:15 | Сообщение # 30 |

|

Главный Администратор

Группа: Администраторы

Сообщений: 320

Награды: 23

Репутация: 222

Статус: Offline

| Коэффициент пересчета может меняться для выхода 2 в пределах 1...10^м (длительность выходных импульсов положительной полярности равна длительности входных), для выхода 1 - в пределах 2...10^м (длительность импульсов отрицательной полярности равна периоду входных импульсов).

Если делитель собран по схеме рис. 34 (б), инвертор DD3 необходимо заменить на двухвходовый элемент И-НЕ, второй вход которого подключить к выходу переноса Р первой микросхемы делителя.

Микросхема ИЕ10 (рис. 38) по своему функционированию аналогична микросхеме ИЕ9 и отличается от нее тем, что считает в двоичном коде, и ее коэффициент пересчета равен 16. В остальном ее работа и правила включения те же.

Микросхема ИЕ11 - десятичный синхронный счетчик (рис. 38). Логика его работы соответствует логике работы счетчиков ИЕ9. Отличие лишь в том, что для сброса в состояние 0 счетчика ИЕ9 необходима подача на вход R лог. 0, а для сброса в состояние 0 счетчика ИЕ11 кроме подачи на вход ER (разрешение уст. 0) лог. 0

необходима подача тактового импульса отрицательной полярности на вход С, по спаду которого и происходит сброс счетчика. Таким образом, все изменения выходных сигналов этой микросхемы происходят по спаду импульсов отрицательной полярности на входе С.

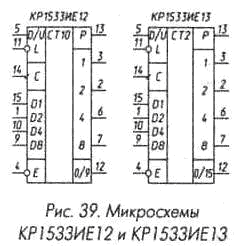

Микросхема КР1533ИЕ12 (рис. 39) обеспечивает параллельную запись и режим счета. Входы Dl, D2, D4, D8 служат для подачи сигналов кода при параллельной записи информации. Запись в триггеры счетчика происходит асинхронно при поступлении на вход L лог. 0 независимо от состояния других входов. При лог. 1 на входе L и лог. 0 на входе разрешения работы Е счетчик изменяет состояние по спадам импульсов отрицательной полярности на входе С. Направление счета определяется сигналом на входе D/U: при лог. 0 происходит счет вверх, при лог. 1 - вниз.

Для построения многоразрядных счетчиков у микросхемы есть два специальных выхода: последнего состояния 0/9 и переноса Р. На выходе 0/9 лог. 1 появляется при достижении состояния 9 при прямом счете и состояния 0 при обратном. В остальных случаях на выходе 0/9 - лог. 0. При наличии лог. 1 на выходе 0/9 и лог. 0 на входе Е одновременно с импульсом на входе С на выходе переноса Р появляется импульс отрицательной полярности и той же длительности.

Счетчик КР1533ИЕ12 не имеет входа установки в 0. Для этой цели на входы Dl, D2, D4, D8 подают лог. 0, а на вход L - импульс отрицательной полярности. Смена сигналов на входах D/U и Е должна происходить в момент переключения сигнала на входе С из лог. 0 в лог. 1 или в паузе между импульсами на входе С (то есть при лог. 1 на этом входе).

Пример временной диаграммы работы счетчика представлен на рис. 40. По импульсу отрицательной полярности на входе L записываются сигналы кода числа 7 в триггеры счетчика (сигналы кода 0111 на входах D8, D4, D2, Dl не показаны). Первые пять импульсов на входе С переводят его последовательно в состояния 8, 9, 0, 1, 2. На выходе 0/9 лог. 1 появляется при переходе счетчика в состояние 9. Импульс на его выходе Р формируется одновременно с третьим импульсом на входе С, по спаду которого счетчик переключается в состояние 0.

В момент окончания пятого импульса происходит смена направления счета изменением сигнала на входе D/U и следующие пять импульсов на входе С переводят счетчик последовательно в состояния 1, 0, 9, 8,7 и т. д. При переходе счетчика в состояние 0 на выходе 0/9 появляется лог. 1, а одновременно с восьмым импульсом на входе С, переключающим счетчик в состояние 9, на выходе Р формируется импульс отрицательной полярности.

Схема соединения микросхем КР1533ИЕ12 в многоразрядный счетчик показана на рис. 41 (а). Из-за последовательного переключения быстродействие такого счетчика в реверсивном режиме снижается относительно быстродействия одной микросхемы.

Если необходим реверсивный счетчик с максимально возможным быстродействием, его собирают по схеме рис. 41 (б). В этом счетчике все триггеры микросхем переключаются одновременно и его быстродействие не зависит от числа разрядов. Однако для каждого десятичного разряда, кроме первого, требуется элемент И-НЕ с числом входов, возрастающим по мере роста номера разряда.

В зависимости от необходимого быстродействия возможно построение различных вариантов последовательно-параллельного счетчика. Можно, например, не использовать выход 0/9 микросхемы DD4 (рис. 41, б), а ее выход Р соединить с входом тактовых импульсов второго такого счетчика.

Микросхема КР1533ИЕ13 (рис. 39) аналогична КР1533ИЕ12, но ее коэффициент пересчета равен 16. Все правила ее использования и схемы включения соответствуют микросхеме КР1533ИЕ12.

|

| |

| |

|